Universidad de Alcalá

Escuela Politécnica Superior

GRADO EN INGENIERÍA ELECTRÓNICA Y

AUTOMÁTICA INDUSTRIAL

Trabajo Fin de Grado

Báscula de pesaje basada en la tarjeta de evaluación

EVAL-AD7195

Autor: Daniel Vacas Fernández

Tutor/es: Francisco Javier Meca Meca

ÍNDICE

Índice de figuras ... 5

Índice de gráficas ... 8

Índice de tablas ... 11

Resumen en castellano ... 13

Resumen en inglés ... 13

Resumen extendido ... 14

Palabras clave ... 16

Introducción ... 17

1. Objetivos del proyecto ... 18

2. Fases de la información ... 19

3. Descripción de los elementos que componen el sistema de medida ... 20

3.1. Célula de carga ... 20

3.1.1. Análisis de una célula de carga... 21

3.2. Características básicas del circuito integrado AD7195 ... 23

3.2.1. Multiplexor ... 24

3.2.2. PGA ... 24

3.2.3. ADC ... 25

3.2.3.1. ADC ∆-Σ ... 28

3.2.3.2. Código de salida del ADC ... 33

3.2.3.3. Configuración unipolar/bipolar ... 34

3.2.3.4. Configuración del filtro digital ... 34

3.2.3.5. Comparativa de modos del filtro digital ... 47

3.2.3.6. Ruido en valor eficaz para distintas ganancias y frecuencia de conversión... 48

3.2.3.7. Métodos de conversión ... 52

3.2.3.8. Proceso de calibración ... 56

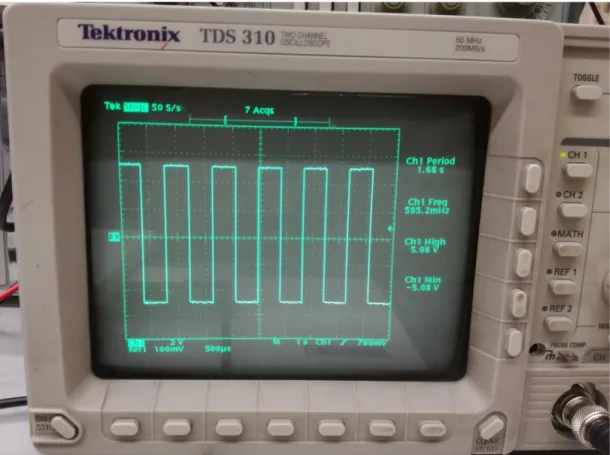

3.2.3.9. Relación entre frecuencias de salida del ADC y del sistema57 3.2.4. Reloj de excitación AC ... 62

3.2.5. Sensor de temperatura ... 64

3.2.6. SPI ... 65

5. Métodos de compensación de offset y efectos de la temperatura ... 68

5.1. Amplificador Lock In ... 69

5.1.1. Estructura de un sistema Lock In ... 70

5.2. Alimentación AC ... 72

6. Elementos hardware ... 74

7. Software de la placa de evaluación AD7195 ... 75

8. Pruebas de laboratorio y resultados ... 81

8.1. Comparativa de diferentes configuraciones de funcionamiento ... 82

Alimentación DC vs alimentación AC ... 82

Comparativa de ganancias ... 84

Configuración del filtro digital ... 89

Frecuencia de salida ADC (valor decimal de FS) ... 90

Polaridad del ADC ... 93

Rechazo 50/60 Hz ... 96

8.2. Tensión de salida de la báscula en función del peso ... 99

8.3. Funcionamiento del sistema expuesto a fuente de error ... 102

8.3.1. Definición de termopar ... 103

8.3.2. Análisis con sistema expuesto a fuente de error ... 104

Alimentación DC vs alimentación AC ... 104

Respuesta del sistema ante diferentes frecuencias de salida del ADC ... 111

Comparativa de ganancias ... 113

Configuración del filtro digital ... 116

Polaridad del ADC ... 123

Modo rechazo 50/60 Hz ... 124

Conclusiones ... 126

Índice de figuras

Figura 1. Célula de carga.

Figura 2. Placa de evaluación AD7195 de Analog Devices Inc.

Figura 3. Esquema gráfico del sistema de medida de peso.

Figura 4. Pieza de célula de carga con galgas y su equivalente eléctrico.

Figura 5. Esquema básico de las tensiones de alimentación y salida de una célula de carga.

Figura 6. Representación gráfica de un puente de Wheatstone de cuatro galgas.

Figura 7. Esquemático completo del circuito integrado AD7195 + circuito de célula de carga.

Figura 8. Esquema básico de un multiplexor.

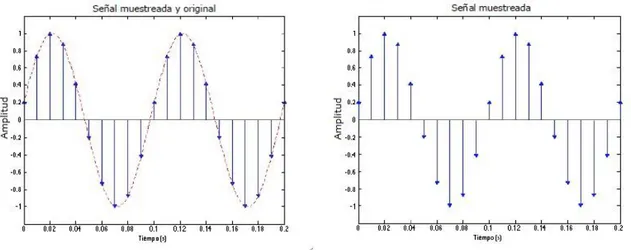

Figura 9. Representación gráfica del proceso de discretización para diferentes frecuencias de muestreo.

Figura 10. Ejemplo de señal sinusoidal analógica y su equivalente digitalizada.

Figura 11. Representación gráfica de filtrado del espectro en baja frecuencia.

Figura 12. Representación gráfica de filtro anti-aliasing.

Figura 13. Escalón de cuantificación.

Figura 14. Distribución del ruido de cuantificación en función de la configuración del sistema de conversión.

Figura 15. Representación gráfica de un ADC delta-sigma.

Figura 16. Ejemplos del modo de funcionamiento del ADC delta-sigma.

Figura 17. Obtención del primer bit del código de salida en un ADC ∆Σ de 4 bits.

Figura 18. Obtención del segundo bit del código de salida en un ADC ∆Σ de 4 bits.

Figura 19. Obtención del tercer bit del código de salida en un ADC ∆Σ de 4 bits.

Figura 20. Obtención del cuarto bit del código de salida en un ADC ∆Σ de 4 bits.

Figura 21. Escalón de cuantificación para el ejemplo de ADC ∆Σ.

Figura 22. Esquema del funcionamiento del modo chop.

Figura 23. Esquema gráfico del ADC modo sinc4 con chop desactivado.

Figura 25. Esquema del funcionamiento con sinc4 y modo latencia activado. Figura 26. Esquema gráfico del ADC modo sinc3 con chop desactivado.

Figura 27.Esquema gráfico de los tiempos de conversión tras cambio de canal con sinc3 (chop off).

Figura 28. Esquema del funcionamiento con sinc3 y modo latencia activado. Figura 29. Esquema gráfico del ADC modo sinc4 con chop activado.

Figura 30. Esquema gráfico del ADC modo sinc3 con chop activado.

Figura 31. Representación de la señal de salida de datos para sinc4, fADC=4,7 Hz (FS=1023).

Figura 32. Representación de la señal de salida de datos para sinc4, fADC=50 Hz (FS=96).

Figura 33. Representación de la señal de salida de datos para sinc4, fADC=4,8 k Hz (FS=1).

Figura 34. Representación de la señal de salida de datos para sinc3, fADC=4,7 Hz (FS=1023).

Figura 35. Representación de la señal de salida de datos para sinc3, fADC=50 Hz (FS=96).

Figura 36. Representación de la señal de salida de datos para sinc3, f

ADC=4,8 k Hz (FS=1).

Figura 37. Esquema completo de la placa de evaluación con la célula de carga.

Figura 38. Esquema del funcionamiento para alimentación AC (fase 1). Tensión (rojo) y referencia (azul).

Figura 39. Esquema del funcionamiento para alimentación AC (fase 2). Tensión (rojo) y referencia (azul).

Figura 40. Esquema de conexiones de leds vinculados a cada tipo de alimentación.

Figura 41. Leds encendidos que indican la configuración de la alimentación.

Figura 42. Dos metales expuestos a diferentes temperaturas en sus uniones, inducen una corriente por efecto Seebeck.

Figura 43. Representación de información de interés mezclado con ruido.

Figura 44. Representación de la señal modulada mezclada con ruido.

Figura 45. Esquema de sistema Lock In.

Figura 46. Comparativa de la señal resultante tras pasar por el multiplicador en Lock In.

Figura 47. Información obtenida por filtro paso-bajo, aislándola del ruido.

Figura 48. Amplificador seguidor con señal de entrada escalón positivo Vin=5V con offset.

Figura 50. Amplificador seguidor con señal de entrada escalón negativo Vin=5V con offset.

Figura 51. Tensión de salida del amplificador de la figura 50 con Vin negativa.

Figura 52. Placa de evaluación AD7195 y célula de carga.

Figura 53. Ventana principal del software de la placa de evaluación AD7195.

Figura 54. Opciones configurables del ADC.

Figura 55. Diferentes opciones que permite el apartado Modo de operación de la placa de evaluación.

Figura 56. Conexiones necesarias para realizar el test de ruido de baja frecuencia.

Figura 57. Configuración de los parámetros predeterminada para el test de ruido.

Figura 58. Evolución del ruido extraído por el sistema a lo largo de 100 muestras.

Figura 59. Pantalla de calibración del sistema de medida.

Figura 60. Valores por defecto del ADC.

Figuras 61 y 62. Comparativa de análisis de resultados para alimentación DC (izquierda) y AC (derecha).

Figura 63. Análisis de resultados para 300 muestras con Ganancia=1.

Figura 64. Análisis de resultados para 300 muestras con Ganancia=32.

Figura 65. Análisis de resultados para 300 muestras con Ganancia=128.

Figura 66. Condiciones para comprobar efecto de la ganancia a la resolución.

Figuras 67 y 68. Análisis de resultados para sinc4 y sinc3, respectivamente. Figura 69. Análisis de resultados para fADC=4,8 kHz (FS=1).

Figura 70. Análisis de resultados para fADC=10 Hz (FS=480).

Figura 71. Análisis de resultados para fADC=4,7 Hz (FS=1023).

Figuras 72 y 73. Resultados extraídos del software para configuración bipolar (izquierda) y unipolar (derecha).

Figuras 74 y 75. Datos de 100 muestras con alimentación AC para configuración bipolar (izquierda) y unipolar (derecha).

Figura 76. Análisis de valores para alimentación DC y rechazo 50 Hz.

Figura 79. Datos aportados por el fabricante de la célula de carga.

Figura 80. Principio de funcionamiento de un termopar.

Figura 81. Primera conexión del termopar en serie con la salida del puente de Wheatstone.

Figura 82. Segunda conexión del termopar en serie con la salida del puente de Wheatstone.

Figuras 83 y 84. Datos relevantes del sistema con alimentación AC en presencia de termopar y configuración bipolar (izquierda) y unipolar (derecha).

Índice de gráficas

Gráfica 1. Respuesta del filtro sinc4 (FS=96). Gráfica 2. Respuesta del filtro sinc4 (FS=80). Gráfica 3. Respuesta del filtro sinc4 (FS=480).

Gráfica 4. Respuesta del filtro sinc4 (FS=96) y REJ60=1. Gráfica 5. Respuesta del filtro sinc3 (FS=96).

Gráfica 6. Respuesta del filtro sinc3 con rechazo 50/60 Hz activo (FS=480).

Gráfica 7. Respuesta del filtro sinc3 con rechazo 50/60 Hz activo (FS=96) y REJ60=1 . Gráfica 8. Respuesta del filtro sinc4 (FS=96) y chop habilitado.

Gráfica 9. Respuesta del filtro sinc4 (FS=96), REJ60=1 y chop habilitado. Gráfica 10. Respuesta del filtro sinc3 (FS=96) y chop habilitado.

Gráfica 11. Respuesta del filtro sinc4 (FS=96), REJ60=1 y chop habilitado.

Gráfica 12. Diagrama de funcionamiento del sistema para modo de conversión simple.

Gráfica 13. Diagrama de funcionamiento del sistema para modo de conversión continua.

Gráfica 14. Representación de la señal AC y los periodos de salida del ADC para sinc4. Gráfica 15. Representación de la señal AC y los periodos de salida del ADC para sinc3. Gráfica 16. Evolución para 300 muestras de la medida con alimentación DC.

Gráfica 17. Evolución para 300 muestras de la medida con alimentación AC.

Gráfica 18. Representación de la repetición de valores de salida para alimentación DC.

Gráfica 20. Histograma con la repetición de los valores para Ganancia=1.

Gráfica 21. Histograma con la repetición de los valores para Ganancia=32.

Gráfica 22. Histograma con la repetición de los valores para Ganancia=128.

Gráfica 23. Histograma con la repetición de valores para 300 muestras con filtro en modo sinc4. Gráfica 24. Histograma con la repetición de valores para 300 muestras con filtro en modo sinc3. Gráfica 25. Histograma con la repetición de valores para fADC=4,8 kHz (FS=1).

Gráfica 26. Histograma con la repetición de valores para fADC=10 Hz (FS=480).

Gráfica 27. Histograma con la repetición de valores para fADC=4,7 Hz (FS=1023).

Gráficas 28 y 29. Histograma para configuración bipolar (superior) y unipolar (inferior).

Gráfica 30 y 31. Comparativa conjunta de la evolución de la señal de salida del sistema con alimentación AC y modo bipolar (superior) y unipolar (inferior).

Gráfica 32 y 33. Histograma de la señal de salida del sistema con alimentación AC y modo bipolar (superior) y unipolar (inferior).

Gráfica 34. Repetición de valores para alimentación DC y rechazo 50 Hz.

Gráfica 35. Repetición de valores para alimentación DC y rechazo 60 Hz.

Gráfica 36. Repetición de valores para alimentación DC y rechazo 50/60 Hz.

Gráfica 37. Evolución de la tensión de salida respecto al peso.

Gráfica 38. Evolución de la señal de salida con alimentación DC bajo efecto de termopar aportando tensión adicional.

Gráfica 39. Evolución de la señal de salida con alimentación DC bajo efecto de termopar que reduce tensión de salida del puente.

Gráfica 40. Evolución de la medida del peso con alimentación AC con caldeo en ON y OFF, respectivamente (conexión 1).

Gráfica 41. Evolución de la medida en gramos para caldeo en ON (conexión 1).

Gráfica 42. Evolución de la medida en gramos para caldeo en OFF (conexión 1).

Gráfica 43. Evolución de la medida del peso con alimentación AC con caldeo en ON y OFF, respectivamente (conexión 2).

Gráfica 44. Evolución de la medida en gramos para caldeo en ON (conexión 2).

Gráfica 46. Evolución de la medida en gramos para ciclos del caldeo en ON y OFF, con fADC=5Hz

(FS=960).

Gráfica 47. Evolución de la medida en gramos para ciclos del caldeo en ON y OFF, con fADC=10Hz

(FS=480).

Gráfica 48. Respuesta del sistema con termopar en conexión 1, ganancia=1 con alimentación DC.

Gráfica 49. Evolución de la medida del peso con alimentación AC con caldeo en ON y OFF, respectivamente, con ganancia =1 (conexión 1).

Gráfica 50. Evolución de la medida en gramos para caldeo en ON, alimentación AC y ganancia=1 (conexión 1).

Gráfica 51. Evolución de la medida en gramos para caldeo en OFF, alimentación AC y ganancia=1 (conexión 1).

Gráfica 52. Evolución de la medida del peso con alimentación AC con caldeo en ON y OFF, respectivamente (conexión 1 y configuración sinc3).

Gráficas 53 y 54. Comparativa del sistema expuesto a termopar con alimentación AC con filtro sinc4 (imagen superior) y filtro sinc3 (imagen inferior).

Gráficas 55 y 56. Representación de la señal exponencial y las muestras para salidas del ADC (fADC=5Hz) con τ entre 1 y 5 para filtro sinc3 (izquierda) y filtro sinc4 (derecha).

Gráficas 57 y 58. Representación de la señal exponencial y las muestras para salidas del ADC (fADC=10Hz) con τ entre 1 y 5 para filtro sinc3 (izquierda) y filtro sinc4 (derecha).

Gráficas 59 y 60. Representación de la señal exponencial y las muestras para salidas del ADC (fADC=50Hz) con τ entre 1 y 5 para filtro sinc3 (izquierda) y filtro sinc4 (derecha).

Gráficas 61 y 62. Comparativa de la evolución de la salida para alimentación AC en presencia de termopar con modo bipolar (superior) y unipolar (inferior).

Gráfica 63. Comportamiento de la señal de salida del sistema con la activación y desactivación del caldeo con modo rechazo 50 Hz activo (FS=96).

Gráfica 64. Comportamiento de la señal de salida del sistema con la activación y desactivación del caldeo con modo rechazo 60 Hz activo (FS=80).

Índice de tablas

Tabla 1. Valor bit de salida del ADC delta-sigma.

Tabla 2. Características de las diferentes configuraciones del filtro digital del ADC.

Tabla 3. Información del filtro del ADC con chop deshabilitado.

Tabla 4. Información del filtro del ADC con chop habilitado.

Tablas 5 y 6. Ruido en valor eficaz considerando ganancia y fADC para sinc3 y sinc 4 (chop off).

Tabla 7. Resolución efectiva considerando ganancia y fADC para sinc 4 (chop off).

Tabla 8. Resolución efectiva considerando ganancia y fADC para sinc 3 (chop off).

Tablas 9 y 10. Ruido en valor eficaz considerando ganancia y fADC para sinc3 y sinc 4 (chop on).

Tabla 11. Resolución efectiva considerando ganancia y fADC para sinc 4 (chop on).

Tabla 12. Resolución efectiva considerando ganancia y fADC para sinc 3 (chop on).

Tabla 13. Configuración de pines para conversión simple y continua.

Tabla 14. Modos adicionales del registro Modo de operación.

Tabla 15. Configuración de pines para distintos tipos de calibración.

Tabla 16. Frecuencias teóricas y prácticas de la señal AC para sinc4. Tabla 17. Frecuencias teóricas y prácticas de la señal AC para sinc3. Tabla 18. Límites de tensión de entrada según el estado del buffer.

Tabla 19. Posibles configuraciones del reloj que regula el sistema.

Tabla 20. Valores de ruido pico-pico en gramos en función de la ganancia del PGA.

Tabla 21. Valores de resolución pico-pico en gramos en función de la ganancia del PGA.

Tabla 22. Datos de interés en función de la configuración del filtro digital del ADC.

Tabla 23. Ruido pico-pico del sistema en función de la frecuencia de salida del ADC.

Tabla 24. Tensiones de salida del puente en función del peso.

Tabla 25. Valores de las tensiones de salida para intervalos de pesos de 0,5 kg.

Tabla 26. Rango de valores de masa en el intervalo con caldeo en ON (conexión 1).

Tabla 29. Rango de valores de masa en el intervalo con caldeo en OFF (conexión 2).

Tabla 30. Valores representativos de la señal con caldeo ON para termopar en conexión 1.

Tabla 31. Valores representativos de la señal con caldeo OFF para termopar en conexión 1.

Tabla 32. Valores representativos de la señal con caldeo ON para termopar en conexión 2.

Tabla 33. Valores representativos de la señal con caldeo OFF para termopar en conexión 2.

Tabla 34. Configuración de parámetro FS y correspondiente fADC para esta prueba.

Tabla 35. Rango de valores de masa en el intervalo con caldeo en ON (DC y ganancia=1).

Tabla 36. Rango de valores de masa en el intervalo con caldeo en OFF (DC y ganancia=1).

Tabla 37. Valores representativos de la señal con caldeo ON para termopar en conexión 1 (ganancia=1).

Tabla 38. Valores representativos de la señal con caldeo OFF para termopar en conexión 1 (ganancia=1).

Tabla 39. Comparativa del sistema expuesto a termopar con alimentación AC con filtro sinc4 (izquierda) y filtro sinc3 (derecha).

Tabla 40. Valores de función exponencial para salidas del ADC en función de τ (sinc3 y fADC=5

Hz).

Tabla 41. Valores de función exponencial para salidas del ADC en función de τ (sinc4 y fADC=5

Hz).

Tabla 42. Valores de función exponencial para salidas del ADC en función de τ (sinc3 y fADC=10

Hz).

Tabla 43. Valores de función exponencial para salidas del ADC en función de τ (sinc4 y fADC=10

Hz).

Tabla 44. Valores de función exponencial para salidas del ADC en función de τ (sinc3 y fADC=50

Hz).

Tabla 45. Valores de función exponencial para salidas del ADC en función de τ (sinc4 y fADC=50

Resumen en castellano

En este proyecto se va a detallar tanto de forma teórica como práctica la realización de una báscula contando con una célula de carga alimentada tanto por tensión continua como por una señal simétrica alterna. Tanto la generación de esta tensión, como el procesamiento de la tensión proporcionada por la célula de carga como respuesta a la fuerza ejercida por una masa conocida, se llevan a cabo a través de la placa de evaluación del integrado AD7195.

Esta placa viene acompañada de un software que permite tanto la interpretación de los resultados de salida del sistema, como la variación de diversos parámetros o su calibración.

Por lo tanto, en esta memoria se van a describir las fases que intervienen desde que se coloca un peso en la báscula hasta que se obtiene el valor de dicho peso, las distintas configuraciones que permite la placa de evaluación y los resultados que se obtengan de trabajar experimentalmente con este sistema.

Por último, se comprobará el funcionamiento del sistema ante una fuente de error simulada, con el fin de conseguir su anulación. Para ello, se pondrá a funcionar el sistema electrónico con alimentación AC, en lugar de la alimentación DC que emplea por defecto, para así lograr que se compensen los errores entre los dos semiperiodos de una señal alterna.

Summary in English (Resumen en inglés)

In this project it is going to be detailed both theoretically and practically the performance of a scale with a load cell powered by both direct current voltage and an alternating symmetric signal. Both the voltage generation, as the processing of the voltage coming from the load cell responding to the force generated by a known mass weight, are done by the AD7195 evaluation board.

This board is accompanied by software that allows both the interpretation of the output results of the system, as well as the variation of various parameters or its calibration.

Therefore, in this report we will describe the phases involved since placing a weight on the scale until the value of that weight is obtained, the different configurations allowed by the evaluation board and the results obtained from work experimentally with this system.

Resumen extendido

El continuo crecimiento de la complejidad de los instrumentos que son necesarios en nuestra vida, hace que la medición de magnitudes cobre una especial importancia. En nuestra vida diaria establecemos comprobaciones de magnitudes (velocidad a la que nos desplazamos en un vehículo, cantidad que echamos de un ingrediente a una comida, nuestro peso en una báscula…).

Esto también ocurre en el ámbito profesional (un médico que comprueba la tensión de un paciente, un ingeniero mide con un multímetro el voltaje que alimenta a un circuito electrónico, un mecánico mide la presión en el pistón de un motor…).

Para todos estos contextos, es exigible que exista un cierto nivel de precisión y exactitud en la medida. En algunos de esos ejemplos, acumular un índice de error no es nada crítico. Pero en otros, el mínimo error puede suponer un problema inaceptable. Por ello, cuando se construye un sistema de medida, se debe establecer cuánto de preciso y exacto es (con su correspondiente tolerancia). Y este punto será evaluado en el desarrollo de este documento.

Para poner en práctica estas valoraciones, se va a realizar un sistema de medida, que consiste en una báscula. Este sistema de medida de masas va a estar formado por:

Célula de carga. Formado internamente por un puente de Wheatstone que transforma el peso, a través de unas galgas deformables, en una tensión.

Figura 1. Célula de carga.

Figura 2. Placa de evaluación AD7195 de Analog Devices Inc.

Para conocer cómo se procesa la información, veremos conceptos relacionados con la electrónica en sistemas de medida, tales como células de carga, ADC… y que se han visto en asignaturas del Grado, como Sistemas Electrónicos Digitales o Instrumentación Electrónica.

Además, se podrá evaluar qué papel cumple cada elemento de aquéllos que intervienen en la transformación de un estímulo analógico como es la tensión de salida del puente de Wheatstone, que hace las veces de balanza, hasta que esa tensión se expresa en formato digital, tras ser procesada, a través de un sistema de comunicación puerto serie que lleva la información hasta un ordenador a través de un cable USB.

Como ya se desglosará durante esta memoria, el realizar un sistema de medida donde se busque una alta precisión trae consigo una serie de dificultades que alejan al sistema de las consideraciones teóricas ideales. Un sistema electrónico está expuesto tanto internamente como en el entorno a distintas circunstancias, que hacen que en un sistema de medición, exista una desviación entre el valor medido y el valor real de una magnitud. La aparición de tensiones de offset asociadas a la tensión de salida de la célula de carga o la exposición del sistema a temperaturas cambiantes son consideraciones que debemos tener en cuenta durante la evaluación de todo el conjunto de medida.

Por ello, se tratará los efectos que producen estas fuentes de error, así como posibles tratamientos para hacer al sistema inmune a estos errores. Principalmente se detallarán dos alternativas para conseguir este propósito: un amplificador Lock In y dotar al sistema de alimentación AC. Este último concepto será el que pondremos en práctica en este proyecto.

Bajo esta influencia, se testeará el sistema tanto con alimentación DC como AC. Según las suposiciones teóricas, el error para alimentación de continua debe ser importante, mientras que para alimentación alterna, el sistema debería ser capaz de compensar el error hasta hacerlo prácticamente inexistente.

Además, debido a la alta versatilidad que ofrece la placa de evaluación, se va a comprobar qué beneficios y qué inconvenientes aportan cada una de las diferentes funcionalidades que ofrece principalmente la configuración del ADC, con el fin de determinar qué configuración global es la más conveniente cuando trabajamos con nuestro sistema de medida particular (mejor inmunidad al ruido, mayor precisión, mayor velocidad, mayor índice de resolución…).

Palabras clave

Célula de carga Sistema de medida

Termopar

Introducción

En la actualidad, con el avance de la ciencia y la tecnología, y con ello de las necesidades tanto personales como profesionales, estamos dotados de sistemas cada vez más sofisticados y complejos. Entran en juego más y más factores que siempre interesa tener cuantificados y controlados.

El hecho de aumentar el número de elementos que intervienen en un proceso hace que se multipliquen los posibles focos de error que se pueden obtener de ellos. Esta circunstancia en algunos contextos puede ser asumible y no afectar al resultado final de forma relevante, pero en procesos en los que se requiera de una alta precisión, la presencia de estos errores es inasumible. Por ello, es necesario conocer su procedencia, su influencia y los posibles métodos para minimizarlos.

En este trabajo, nos vamos a adentrar más concretamente en el campo de la medida de una magnitud.

Cualquier aparato que empleemos para la obtención de una medida requiere de altos niveles de precisión y exactitud; esto es, obtener para varias medidas en diferentes instantes de tiempo un valor similar ante el mismo estímulo, y que el valor que se desprenda de la medida sea lo más cercano posible a su valor real.

Sin embargo, la obtención totalmente exacta de un valor medido es un concepto ideal, imposible de alcanzar en la realidad. Muchos factores (algunos cuantificables y otros no) impiden que se pueda conseguir. Puede abarcar desde una mala calibración del instrumento, pasando por una mala manipulación del operario, hasta la desviación producida por la acumulación de las tolerancias y derivas de los distintos componentes.

Otros factores, como pueden ser un offset indeseado o los efectos producidos por la exposición del sistema a una temperatura variable también afectan y deben ser tenidos en cuenta. Durante esta memoria, se cuantificará cuánto afectan estos fenómenos para así ser tenidos en cuenta para poder ser contrarrestados y que su aportación al resultado final sea reducido y así, conseguir el valor lo más exacto posible.

En este Trabajo de Fin de Grado, se va a utilizar como sistema de medida una balanza, basada en una célula de carga (puente de Wheatstone), alimentada con una tensión, que en función de la configuración elegida, podrá ser continua o alterna.

Por la acción del peso que se coloque sobre la balanza, se generará una tensión a la salida del puente que será procesada mediante el circuito integrado AD7195. Tras este procesamiento de la señal procedente de la báscula, se obtendrán los valores más relevantes obtenidos de las medidas a través del software característico de la placa de evaluación AD7195 con la que se va a trabajar.

Entre estos parámetros a configurar se encuentran desde la forma de excitación del circuito electrónico (que como ya se ha comentado, puede ser continua o alterna, y que se obtienen a través de la propia placa de evaluación), limitar o no el número de muestras de la salida digital, o múltiples opciones de configuración que ofrece el propio ADC y el filtro digital asociado a él, como veremos más tarde.

1. Objetivos del proyecto

Describir los elementos básicos que componen un sistema de medida. Aportar una breve descripción teórica de todos los elementos que componen este sistema de medida particular y los diferentes modos de funcionamiento en los que pueden trabajar algunos de ellos.

Conocer las posibles funcionalidades y los elementos que componen el circuito integrado AD7195 de Analog Devices Inc elegido para este proyecto.

Analizar las distintas configuraciones que permite el circuito integrado y los efectos que producen cada una de ellas.

Sistema de pesaje con alimentación DC-AC

En este texto se va a detallar la composición de un sistema de medida de peso. Para ello, se va a utilizar una placa de evaluación con el circuito integrado AD7195 incluido en él. Aunque principalmente su funcionalidad es la de procesar la información en un sistema de pesaje de alta precisión, su versatilidad permite realizar otros sistemas de medida.

Todos los elementos que se necesitan para la elaboración del sistema de medida son:

Placa de evaluación AD7195EBZ (con display incluido).

Cable de comunicación USB placa-PC.

CD de instalación de “AD719x Evaluation Board Software”.

Fuente de alimentación (aunque el sistema también se puede alimentar a través del cable USB conectado al ordenador).

2. Fases de la información

La información, desde que es generada por la balanza al colocar el peso, hasta que obtenemos por pantalla los datos obtenidos para conseguir el valor de la medición, pasa por una serie de elementos electrónicos que componen la placa de evaluación AD7195, hasta que finalmente se manifiesta en la pantalla del ordenador donde opera el software asociado a la placa.

Figura 3. Esquema gráfico del sistema de medida de peso.

Por ello, de forma secuencial, la trayectoria de la información es la siguiente:

Se coloca una pesa de valor conocido sobre la báscula. Esto generará una tensión diferencial de salida que se lleva al integrado AD7195. En este caso, a los terminales de entrada de un multiplexor analógico. Está dotado de cuatro canales de entrada, pero sólo se requieren de los dos que constituyen la previamente citada salida diferencial de la célula de carga.

La señal de salida del multiplexor se lleva a un chip PGA (Programmable Gain Amplifier), que puede amplificar la señal con distintas ganancias, en función de las necesidades de la aplicación. Como se detalla en el apartado de descripción de los distintos elementos del circuito, el rango de posibles ganancias es variado, permitiendo hasta seis configuraciones distintas.

Tras pasar la información por el PGA, es el ADC el encargado de la transformación de la lectura de formato analógico a digital. Para ello, el integrado AD7195 consta de un modulador delta-sigma (∆-Σ) de cuarto orden, seguido de un filtro digital. Esta operación permite discretizar la señal, que aporta beneficios en cuanto a la facilidad para trabajar con la señal como la mitigación de errores procedentes del ruido.

Una vez se ha generado la señal digital, ya sólo queda que la información sea observable a la salida. Para ello, la placa de evaluación utiliza un protocolo de comunicación SPI. Con ello, a través de un cable USB, la información pasa de la placa al ordenador que tengamos conectado al cable. Con éste, podremos establecer las distintas configuraciones posibles y observar los resultados obtenidos a través del software oficial proporcionado por el propio fabricante de la placa de evaluación.

3. Descripción de los elementos que componen el

sistema de medida

3.1. Célula de carga

Es el primer elemento que interviene en nuestro sistema. Es un dispositivo para medir fuerza que integra un elemento mecánico que convierte la fuerza en deformación y unas galgas extensométricas pegadas que miden dichas deformaciones. Estas galgas son dispositivos electrónicos empleados para transformar la deformación a la que se expone la pieza en una variable eléctrica. Según las características de la pieza, se pueden construir balanzas con fondos de escala desde gramos hasta cientos de toneladas, con exactitudes muy elevadas.

Una célula de carga puede tener múltiples posibles aplicaciones, entre las que se encuentra la que se va a realizar consistente en una báscula de pesaje.

Cuando una célula de carga trabaja como báscula electrónica, se producen varios procesos. Al ubicar un peso sobre la báscula, la fuerza que ejerce sobre la pieza produce una deformación. Esta deformación es medida a través de las galgas extensométricas, adosadas a la pieza, que presentan una resistencia eléctrica función de la deformación a la que son sometidas.

Figura 5. Esquema de las tensiones de alimentación y salida de una célula de carga.

Se distinguen dos tensiones, que según la notación de la Figura 5 son:

Vexc: Es la tensión de alimentación del puente. Esta tensión depende de las

necesidades de la aplicación, y se puede obtener de los pines de la placa de evaluación o bien, mediante una fuente de alimentación externa.

Vs: tensión de salida del puente. Esta tensión será la información que será procesada

por el circuito integrado. Depende del estímulo de entrada, que en nuestro caso será la fuerza que ejerza un peso sobre la báscula compuesta por la célula de carga.

3.1.1. Análisis de una célula de carga

Para conocer la tensión de salida del puente, se aplica superposición de divisores de tensión:

𝑂𝑢𝑡+=

𝑅3

𝑅2+ 𝑅3

𝑉𝑐𝑐

𝑂𝑢𝑡−=

𝑅4

𝑅1+ 𝑅4

𝑉𝑐𝑐

𝑉𝑆 = 𝑂𝑢𝑡+− 𝑂𝑢𝑡−

Sustituimos los términos previamente definidos:

𝑉𝑆 = 𝑉𝑐𝑐

𝑅3

𝑅2+ 𝑅3

− 𝑅4 𝑅1+ 𝑅4

𝑉𝑆 = 𝑉𝑐𝑐

𝑅1𝑅3− 𝑅2𝑅4

𝑅2+ 𝑅3 (𝑅1+ 𝑅4)

El principio de funcionamiento de una célula de carga se fundamenta en la deformación de sus galgas al aplicarse una fuerza sobre la pieza a la que van adosadas. Por lo tanto, el valor de las resistencias que las componen está parametrizado por la masa que se encuentre sobre la báscula.

Si suponemos un comportamiento de variación lineal de las galgas que componen el puente de Wheatstone, obtenemos que el valor de cada resistencia puede quedar modelada como:

𝑅1= 𝑅3= 𝑅𝑥 = 𝑅𝑂 1 + 𝐾𝑥

𝑅2= 𝑅4 = 𝑅_𝑥 = 𝑅𝑂 1 − 𝐾𝑥

donde K es la sensibilidad propia de cada galga y x se corresponde con la elongación, función de la masa ubicada sobre la báscula.

Si sustituimos estas condiciones en la expresión previa en la que se obtenía la tensión de salida del puente, obtenemos:

𝑉𝑆 = 𝑉𝑐𝑐

𝑅𝑂2 1 + 𝐾𝑥 2− 𝑅𝑂2 1 − 𝐾𝑥 2

𝑅𝑂 1 − 𝐾𝑥 + 𝑅𝑂(1 + 𝐾𝑥) 𝑅𝑂 1 + 𝐾𝑥 + 𝑅𝑂(1 − 𝐾𝑥)

𝑉𝑆 = 𝑉𝑐𝑐

𝑅𝑂2 1 + 𝐾𝑥 2− 1 − 𝐾𝑥 2

𝑅𝑂− 𝑅𝑂𝐾𝑥 + 𝑅𝑂+ 𝑅𝑂𝐾𝑥 𝑅𝑂+ 𝑅𝑂𝐾𝑥 + 𝑅𝑂 − 𝑅𝑂𝐾𝑥

𝑉𝑆 = 𝑉𝑐𝑐

𝑅𝑂2 1 + 𝐾2𝑥2+ 2𝐾𝑥 − 1 − 𝐾2𝑥2+ 2𝐾𝑥

2𝑅𝑂· 2𝑅𝑂

𝑉𝑆 = 𝑉𝑐𝑐

4𝐾𝑥𝑅𝑂2

4𝑅𝑂2

La tensión de salida de la galga (Vs) será la que se lleve al ADC del integrado para su procesamiento.

Un parámetro que tiene una especial importancia es la sensibilidad. Se define como la derivada de la salida en función de la deformación función del peso; es decir, cuánto varía la salida ante una variación de la entrada. Conocemos la sensibilidad de cada galga, que hemos definido con la variable K, pero también es interesante conocer la sensibilidad del conjunto completo. Lo definimos como Sp (sensibilidad del puente).

𝑆𝑝 =

𝑑𝑉𝑆

𝑑𝑥 = 𝑉𝑐𝑐· 𝐾

La magnitud de la sensibilidad se expresa en mV/Kg, o también en mV/V del fondo de escala (según interese), y es directamente proporcional a la sensibilidad de cada galga y la tensión de alimentación. Este parámetro es uno de los más importantes de entre los que caracterizan a una célula de carga.

3.2. Características básicas del circuito integrado AD7195

El circuito integrado AD7195 posee características que lo hacen idóneo para aplicaciones de sistemas de medida donde prima la búsqueda de la precisión. La información obtenida se procesa transformándola en información digital a través de un conversor analógico-digital tipo delta-sigma de 24 bits. Además, el integrado posee la capacidad de generar una fuente de alimentación en corriente alterna a partir de una de continua. Su versatilidad permite que su empleo sea una opción adecuada en múltiples aplicaciones como medidas de temperaturas, presiones, pesos, etc.

Recurriendo a las hojas de características del integrado, podemos destacar algunas de sus características principales:

· Excitación DC o AC · Bajo nivel de ruido

· 2 canales de entrada diferenciales o 4 canales pseudodiferenciales · Ganancia programable

· Reloj interno/externo · Fuente de tensión

Tensión analógica: 4,75/5,25 V Tensión digital: 2,7/5,25 V · Consumo: corriente nominal de 6 mA

· Intervalo de temperaturas entre -40˚C y +105˚C

Figura 7. Esquemático completo del circuito integrado AD7195 + circuito de célula de carga.

Aunque la placa de evaluación está compuesta por un elevado número de componentes que intervienen en el procesamiento de la información, a continuación se destacan los más relevantes, para conocer mejor cómo operan.

3.2.1. Multiplexor

En el integrado AD7195, el multiplexor analógico está dotado de cuatro entradas, aunque para los requerimientos de nuestra aplicación, sólo se necesitan dos de ellas. El programa para la evaluación del circuito integrado con el que operaremos permite elegir qué canales queremos habilitar, como veremos más adelante.

Figura 8. Esquema básico de un multiplexor.

3.2.2. PGA

Este bloque de ganancia programable exige una condición de máxima amplitud de la señal de entrada, siguiendo la expresión ±(𝐴𝑉𝐷𝐷− 1,25𝑉)/𝑔𝑎𝑛𝑎𝑛𝑐𝑖𝑎. Así pues, la máxima señal de la

entrada diferencial sería con ganancia la unidad. Si la tensión de alimentación analógica es AVDD=5 V, esta tensión sería 3,75 V en modo unipolar y ±3,75 V en modo bipolar.

3.2.3. ADC

Es un Conversor Analógico-Digital. La señal de entrada a éste se encuentra en formato analógico y el ADC se encarga de discretizar la señal, tomando un número de muestras periódicas en el tiempo. Este periodo de muestreo debe ser seleccionado cuidadosamente, puesto que si es demasiado el tiempo entre muestra y muestra, se puede perder información relevante de la señal.

El bloque que consideramos con ADC, está compuesto de un ADC delta-sigma de 24 bits y un filtro digital.

El filtro digital existente en el AD7195 ofrece gran versatilidad, puesto que posee cuatro modos de funcionamiento, regulado por dos pines. El dispositivo puede funcionar con filtro sinc3 o sinc4, con chop habilitado o deshabilitado y con modo latencia cero operativo o no.

Posteriormente, se detallarán las características de las distintas configuraciones posibles del filtro asociado al ADC.

¿Cómo actúa un ADC?

Así pues, una señal analógica muestreada y la señal discreta digitalizada tendrían la siguiente apariencia:

Figura 10. Ejemplo de señal sinusoidal analógica y su equivalente digitalizada.

De primeras, no parece ventajoso reducir la cantidad de datos con los que trabajamos. Sin embargo, es un paso necesario, puesto que la funcionalidad de este proceso es facilitar el procesamiento y hacer que la señal digital que se obtiene tras este tratamiento resulte más blindada a efectos no deseados, como ruidos o interferencias, a las que son más sensibles las señales analógicas.

Se puede pensar que si queremos discretizar una señal y obtener una resultante de gran calidad, basta con utilizar un bajo periodo de muestreo (alta frecuencia de muestreo). Sin embargo, hay que tener en cuenta y valorar un fenómeno indeseado que puede producir pérdida de información de la señal analógica original, conocido como aliasing.

El aliasing es un fenómeno que provoca que una señal no se discretice correctamente en su paso de analógica en el origen a digital. Es decir, si esto sucede, no se podría obtener la señal original de partida a partir de la que hemos conseguido digitalizar.

Si definimos la frecuencia de la señal de muestreo como fs, el espectro de la señal muestreadora es un tren de deltas con frecuencias múltiplos de fs, por lo que el resultado del producto tendrá un espectro con energía en las frecuencias de los valores suma y diferencia de las frecuencias de la señal muestreadora y la muestreada.

Figura 11. Representación gráfica de filtrado del espectro en baja frecuencia.

El espectro de una señal finita en el tiempo es infinito en frecuencia. Si la distancia entre muestras no es adecuada, se pueden solapar la información entre espectros.

Para evitar este inconveniente, se debe tener en cuenta el llamado Criterio de Nyquist. Según este principio, la frecuencia de muestreo debe ser al menos dos veces superior al ancho de banda de la señal. Otra forma de verlo es quela frecuencia máxima de la señal de entrada debe ser menor que o igual a la mitad de la frecuencia de muestreo.

Para evitar solapamiento, existen varias alternativas:

Un ancho de banda infinito, con fs infinito. Imposible de realizar en la realidad.

Eliminar la energía de alta frecuencia, puesto que la información principal no transita en esa franja.

La teoría es ésa, pero… ¿cómo conseguirlo en la práctica? A través de un filtro antialiasing. Este filtro consiste en un filtro paso-bajo que reduce la componente espectral de alta frecuencia (mayores frecuencias que la frecuencia de Nyquist), y así, limita el aliasing. La placa de evaluación AD7195 contiene un filtro antialiasing en cada entrada analógica constituida por un circuito RC.

Sin embargo, el solapamiento no debe suponer un problema en particular en el sistema de medida que se va a analizar, puesto que la fs característica de los convertidores ADC Σ-∆ es lo suficientemente elevada como para evitar que dos espectros acaben solapándose.

Figura 12. Representación gráfica de filtro anti-aliasing.

3.2.3.1. ADC ∆-Σ

La placa de evaluación AD7195 utiliza un ADC delta-sigma de 24 bits. Ofrece unas características que le hacen uno de los más utilizados en aplicaciones de medida donde se exige un alto nivel de precisión.

Este tipo de convertidores ofrecen en su salida la diferencia entre la entrada analógica y el valor acumulado tras las conversiones, que puede tener dos estados: positivo (se representa con un 1 lógico) o negativo (0 lógico). Esto supone por tanto un incremento (que se representa matemáticamente por delta ∆).

Para llegar al valor de entrada se utiliza un integrador, de modo que se acumula cada bit alto (valor 1) y se resta cada bit bajo (valor 0), siendo el valor final de esta integración el exceso de unos-ceros de la salida del modulador. Esta etapa integra el valor que recibe desde la anterior; es decir, suma (que matemáticamente se representa por sigma Σ).

Para destacar la ventaja que ofrece este conversor frente a otros, hay que adentrarse levemente en conceptos teóricos.

Si se habla de resolución de un convertidor, un parámetro muy importante es el escalón de cuantificación q, que hace referencia a la diferencia en la magnitud de entrada que representa un cambio de bit en la salida.

Figura 13. Escalón de cuantificación.

Fuente: http://www.sapiensman.com/tecnoficio/docs/doc39.php

La relación señal-ruido sigue la expresión:

𝑆𝑁𝑅 = 6,02 · 𝑛 + 1,76

para una señal sinusoidal de máxima amplitud y donde n representa el número de bits del ADC. Sin embargo, en presencia de ruido, ese número de bits no representará su valor ideal, sino que será menor, y que queda representado por el ENOB o Número Efectivo de Bits:

𝐸𝑁𝑂𝐵 =𝑆𝑁𝑅 − 1,76 𝑑𝐵 6,02 𝑑𝐵

Si se procede a realizar un sobremuestreo (incrementar la frecuencia de muestreo un factor K), el ruido de cuantificación en valor eficaz se mantiene en q/√12, pero ahora ese ruido está distribuido en un ancho de banda K veces mayor (Kfs/2). Si después se emplea un filtro paso bajo, se eliminará el ruido de cuantificación por encima de la frecuencia sobre la que se aplique. De esta forma, se mejora la resolución efectiva en n bits siendo K=22·∆n.

Una vez el filtro digital reduce el ancho de banda, la frecuencia de salida puede ser menor que la frecuencia original (Kfs), satisfaciendo siempre la condición de Nyquist. Esto se puede conseguir aportando a la salida cada resultado múltiplo de un factor y descartar el resto. Este factor puede tener cualquier valor que permita que la frecuencia de salida del ADC sea más de dos veces superior al ancho de banda de la señal. Es lo que se conoce por decimation y no supone pérdida alguna de información (Figura 14(B)).

La explicación básica del funcionamiento de un conversor analógico-digital Σ∆ es la de un codificador. El ADC va a comparar la señal digital de salida (basada en “0” y “1”) con la señal analógica de entrada. Si el valor de la entrada es superior al valor digital previo, la salida será un “1”, mientras que si en la comparación, el valor de entrada es inferior al valor de salida del ciclo anterior, el nuevo bit de salida será “0”.

Su diagrama de operación se corresponde con la siguiente imagen:

Figura 15. Representación gráfica de un ADC delta-sigma.

La secuencia de la información es la siguiente:

1. El ADC capta la señal analógica de entrada y le resta el valor procedente del DAC (±Vref, en función del valor del bit previo).

2. Se integra el valor de la salida del sumador (se obtiene un promedio de los distintos valores de entrada del integrador).

3. Se compara la señal resultado de la integración con un valor predeterminado en el terminal de referencia del comparador (en este caso, 0 V). Como resultado de la comparación, se obtendrá un 1 o un 0.

Condición Valor bit de salida del

comparador

Tensión salida integrador > Tensión ref. comparador 1 Tensión salida integrador < Tensión ref. comparador 0

Tabla 1. Valor bit de salida del ADC delta-sigma.

4. El valor de este bit se lleva a un DAC, que tendrá salida de +Vref en caso de que el valor del bit procedente del comparador sea 1, y -Vref en caso de el valor del bit fuese 0.

5. De nuevo, se inicia un nuevo proceso de comparación (también se incrementa el contador de bits).

de su cuenta (overflow o rebosamiento) se debe resetear tanto el contador como el modulador, de forma que comienza una nueva conversión.

Para entender mejor el funcionamiento, se muestran dos ejemplos gráficos:

Figura 16. Ejemplos del modo de funcionamiento del ADC delta-sigma.

En los ejemplos de la Figura 16, la representación A representa las señales de entrada al comparador; es decir, la salida que va promediando el integrador y la referencia, mientras B supone la salida del comparador, función de las dos anteriores.

Para aclarar su funcionamiento paso a paso, se trata un ejemplo con tensión continua de entrada de 1 V y una tensión de referencia de Vref de ±5 V para un ADC ∆Σ de 4 bits.

Para la obtención del primer bit, se toma el valor de 1V, que se añade como primer término del sumatorio del integrador y puesto que es >0, el comparador genera un bit positivo, que genera una tensión de salida del DAC de +Vref. De esta forma, la situación antes de una nueva muestra es la siguiente:

Figura 17. Obtención del primer bit del código de salida en un ADC ∆Σ de 4 bits.

Figura 18. Obtención del segundo bit del código de salida en un ADC ∆Σ de 4 bits.

Entendido el funcionamiento, para llegar a los 4 bits, quedarían dos procesos análogos a los anteriores, que tendrían por resultado:

Figura 19. Obtención del tercer bit del código de salida en un ADC ∆Σ de 4 bits.

Figura 20. Obtención del cuarto bit del código de salida en un ADC ∆Σ de 4 bits.

que discretizar la tensión analógica de entrada. Por otro lado, el rango de posibles tensiones de entrada está delimitado por ±Vref=±5 V; es decir, 10 V.

Por lo tanto, el escalón de cuantificación q tiene un valor de 10/16=0,625 V. Considerando el error de cuantificación de q/2, la disposición de la función de transferencia de cuantificación se aprecia en la figura 21. Así pues, la tensión de entrada Vin=1 V queda representada en el décimo escalón (el décimo escalón corresponde a valores entre 0,9375 V y 1,5625 V).

Figura 21. Escalón de cuantificación para el ejemplo de ADC ∆Σ.

3.2.3.2. Código de salida del ADC

La salida digital del ADC se realiza mediante códigos. Estos códigos son los que se atribuyen a cada posible valor discreto de la señal siguiendo los escalones de cuantificación que se han mostrado en el apartado anterior. Cada código digital tiene asociado un rango de posibles valores analógicos a la entrada del ADC que en su salida supondrían un mismo código de salida. De esta forma, cuantos más bits disponga el ADC para la representación digital, ante un mismo intervalo de valores analógicos a representar, menor será el error asociado a la cuantificación.

De esta forma, si el ADC está configurado en modo unipolar, el código sólo podrá representar valores decimales positivos. La expresión del código digital para este régimen de funcionamiento es:

𝐶ó𝑑𝑖𝑔𝑜𝑢𝑛𝑖𝑝𝑜𝑙𝑎𝑟 =

En caso de que el modo de funcionamiento sea bipolar, también hay que contemplar valores negativos de tensión. Por ello, la expresión varía:

𝐶ó𝑑𝑖𝑔𝑜𝑏𝑖𝑝𝑜𝑙𝑎𝑟 = 2𝑁−1· 𝐴𝐼𝑁 ·

𝐺𝑎𝑛𝑎𝑛𝑐𝑖𝑎 𝑉𝑅𝐸𝐹

+ 1

En estas expresiones:

N es el número de bits de representación del ADC

AIN es la tensión de salida del multiplexor (entrada al ADC tras su paso por el PGA)

Ganancia es la programable en el PGA (1, 8, 16, 32, 64 ó 128)

VREF es la diferencia de tensión que alimenta el puente de Wheatstone que actúa como

célula de carga y también es la tensión vinculada al ADC, para fijar su SPAN, y por consiguiente, su escalón de cuantificación q.

3.2.3.3. Configuración unipolar/bipolar

El ADC tiene dos configuraciones en cuanto al rango de posibles valores, pudiendo estar configurado como unipolar o bipolar. Sin embargo, y a pesar de lo que se pueda pensar de primeras, la configuración bipolar no implica necesariamente que se admita valores negativos de tensión de entrada respecto a la masa o referencia del sistema. Dependerá del modo de funcionamiento con el que trabaje.

En modo pseudodiferencial, la tensión de referencia es la que se encuentre en AINCOM. Existirá una diferencia de tensión de AINCOM/ganancia en modo unipolar y de ±AINCOM/ganancia en modo bipolar, respecto a AINCOM. Por ejemplo, si la tensión en AINCOM es de 2,5 V con ganancia del amplificador de ganancia programable 2, el rango en unipolar será [2,5V; 3,75V] y en bipolar [1,25V; 3,75V].

En modo diferencial (nuestra configuración por defecto), la tensión de referencia del ADC será la tensión del terminal negativo de la alimentación de la célula de carga (en nuestro caso, coincide con la masa analógica AGND).

3.2.3.4. Configuración del filtro digital

El filtro digital del integrado AD7195 ofrece una gran versatilidad, con varios modos de aplicación. Puede funcionar con filtro en modo sinc3 o sinc4, con modo cero latencia habilitada o no, y con modo de chopeo habilitado o deshabilitado.

Modo chop

La acción de chopping es una técnica empleada en el campo de la electrónica para minimizar en lo posible errores de offset, derivas producidas por este error, y otros errores relacionados con señales de baja frecuencia.

Un error de offset que se produce dentro de los diversos amplificadores del modulador Σ-Δ generalmente puede anularse, ya sea mediante corte local o una puesta a cero automática del amplificador. Sin embargo, otros errores de offset no se pueden eliminar con estos métodos. La solución implementada en estos ADC es realizar un cortocircuito en la entrada dentro de los ADC. Esto elimina cualquier error de desplazamiento y baja frecuencia, lo que resulta en errores de desplazamiento extremadamente bajos y deriva de error de desplazamiento.

Figura 22. Esquema del funcionamiento del modo chop.

La entrada diferencial llevada al modulador se invierte alternativamente (es decir, es chopeada) en la entrada del multiplexor y una conversión del ADC es realizada por cada proceso de chop. Tras pasar por el modulador, la señal pasa por otro multiplexor que invierte la señal antes de pasar al filtro digital.

Si el offset se representa como Vos, la salida cuando chop es 0 es:

𝑉1= 𝑉𝐼𝑁 + − 𝑉𝐼𝑁 − = 𝐴𝐼𝑁 + − 𝐴𝐼𝑁 − + 𝑉𝑂𝑆

y la salida cuando chop es 1 es:

𝑉2= 𝑉𝐼𝑁 + − 𝑉𝐼𝑁 − = − 𝐴𝐼𝑁 + − 𝐴𝐼𝑁 − + 𝑉𝑂𝑆

De la resta de las tensiones de ambas expresiones en el filtro digital se obtiene:

𝑉𝑐𝑜𝑚𝑝𝑒𝑛𝑠𝑎𝑑𝑎 =

𝑉1− 𝑉2

2 = 𝐴𝐼𝑁 + − 𝐴𝐼𝑁 −

con lo que queda eliminado el error de offset.

Chop deshabilitado

Modo filtro SINC

4(chop deshabilitado)

Cuando se alimenta el AD7195, éste es el modo de funcionamiento por defecto.

Cuando trabaja en este modo de sinc4, ofrece unas características respecto al modo sinc3 que son:

+ Excelente tratamiento del ruido para cualquier valor del rango de entrada.

+ Es el modo que ofrece mejor rechazo 50/60 Hz.

+ Mayor precisión.

- Mayor tiempo de establecimiento que sinc3.

Figura 23. Esquema gráfico del ADC modo sinc4 con chop desactivado.

La frecuencia de salida de datos del ADC sigue la siguiente expresión:

𝑓𝐴𝐷𝐶 =

𝑓𝐶𝐿𝐾

1024 · 𝑉𝑎𝑙𝑜𝑟 𝑑𝑒𝑐𝑖𝑚𝑎𝑙 𝐹𝑆

donde:

- fADC es la frecuencia de conversión del ADC.

- fCLK es la frecuencia del reloj maestro (4,92 MHz de valor nominal).

- FS es el valor decimal equivalente a la combinación binaria obtenida de entre los pines FS0 y FS9 del denominado registro de modo, de tal forma que se puede así adecuar la velocidad de salida de datos a las necesidades que requiera nuestra aplicación.

- 1024 es el máximo valor alcanzable por FS (10 bits→210=1024).

Existe un registro de 24 bits, que en la hoja de características de la placa de evaluación lo define el fabricante como “Mode Register (Registro de Modo)”, donde 10 bits (FS9…FS0) se encargan de otorgar un valor a este parámetro. No sólo establece la frecuencia de salida del ADC, sino también la frecuencia de corte del filtro digital asociado al ADC y la frecuencia del primer notch de dicho filtro.

El tiempo de establecimiento para esta configuración sigue la siguiente expresión:

𝑡𝑒𝑠𝑡𝑎𝑏𝑙𝑒𝑐𝑖𝑚𝑖𝑒𝑛𝑡𝑜 (𝑠𝑖𝑛𝑐4)= 4

𝑓𝐴𝐷𝐶

En el momento en el que se produce un cambio de canal, tanto el modulador como el filtro se resetean. Para realizar la primera conversión tras cambio de canal, se requiere del tiempo de establecimiento para completarse (por ello, los primeros cuatro resultados no serán válidos). Una vez se ha producido esta conversión, las siguientes requerirán sólo de 1/fADC.

Figura 24. Esquema gráfico de los tiempos de conversión tras cambio de canal con sinc4 (chop off).

Modo Latencia Cero (sinc

4)

Con este modo de operación, seleccionable simplemente con la activación de un bit (bit 11 del Registro de Modo), se hace al sistema independiente de si trabaja con uno o varios canales en cada conversión. Así, se unifica el tiempo de conversión para ambos casos a:

𝑓𝐴𝐷𝐶 =

1

𝑡𝑒𝑠𝑡𝑎𝑏𝑙𝑒𝑐𝑖𝑚𝑖𝑒𝑛𝑡𝑜 (𝑠𝑖𝑛𝑐 4)

= 𝑓𝐶𝐿𝐾 4 · 1024 · 𝐹𝑆

En el caso de tener una entrada analógica constante o si se produce un cambio de canal, se habilita la conversión a una frecuencia de salida del ADC independiente de si se muestrea una o varias señales. Cuando se realiza una conversión en un solo canal y se genera un escalón en la señal del canal de entrada, el ADC realiza la conversión si el escalón está sincronizado con el proceso de conversión. Si el escalón es asíncrono, se produce una conversión incorrecta.

Rechazo 50 Hz/60 Hz (sinc

4)

Si suponemos que el registro FS tiene un valor de 96 y basados en el reloj interno de 4,92 MHz, con el modo de latencia cero desactivado, la frecuencia de salida del ADC es de 50 Hz (la empleada en las redes eléctricas mundiales, excepto América y algunos países asiáticos).

Activado este régimen de funcionamiento, se produce un rechazo en esta frecuencia y múltiplos de ésta. Por otro lado, si además de este modo, está activo el modo latencia cero, esta frecuencia se divide entre 4 (12,5 Hz).

Gráfica 1. Respuesta del filtro sinc4 (FS=96).

Gráfica 2. Respuesta del filtro sinc4 (FS=80).

Si quisiésemos que nuestro sistema tuviese una versatilidad mundial, requeriríamos de una configuración de FS que permita obtener una frecuencia de salida del ADC divisor de ambos. En nuestro caso, seleccionamos 10 Hz, con FS = 480 (con modo latencia cero, 2,5 Hz).

Gráfica 3. Respuesta del filtro sinc4 (FS=480).

Gráfica 4. Respuesta del filtro sinc4 (FS=96) y REJ60=1.

Este modo de funcionamiento ofrece como ventaja un mayor ancho de banda, pero desarrolla un menor rechazo en alta frecuencia.

Modo filtro SINC

3(chop deshabilitado)

Este filtro tiene un buen comportamiento frente al ruido para frecuencias de salida superiores a 1 kHz. Tiene un rendimiento medio en cuanto al tiempo de establecimiento y al rechazo de frecuencias 50/60 Hz.

Figura 26. Esquema gráfico del ADC modo sinc3 con chop desactivado.

La frecuencia de salida está en el rango entre 4,7 Hz y 4,8 kHz, equivalente en código decimal de los bits de FS a valores comprendidos entre 1 y 1023. La expresión de esta frecuencia es igual a la del filtro modo sinc4, pero el tiempo de establecimiento es menor.

𝑓𝐴𝐷𝐶 =

𝑓𝐶𝐿𝐾

𝑡𝑒𝑠𝑡𝑎𝑏𝑙𝑒𝑐𝑖𝑚𝑖𝑒𝑛𝑡𝑜 (𝑠𝑖𝑛𝑐3)= 3

𝑓𝐴𝐷𝐶

De nuevo, al igual que con el modo sinc4, cuando se produce un cambio de canal, requiere de un tiempo de establecimiento (en este caso, menor que con sinc4), y para conversiones sucesivas, el sistema requerirá de 1/fADC.

Figura 27.Esquema gráfico de los tiempos de conversión tras cambio de canal con sinc3 (chop off).

Modo Latencia Cero (sinc

3)

En este modo, la frecuencia de salida de datos del ADC sigue la expresión:

𝑓𝐴𝐷𝐶 =

𝑓𝐶𝐿𝐾

3 · 1024 · 𝐹𝑆

Cuando la entrada analógica es constante o se produce un cambio de canal, las conversiones son válidas para una frecuencia constante de salida de datos del ADC.

Cuando las conversiones se realizan en un solo canal y se produce un escalón de cambio de valor de entrada analógica, el ADC realiza una conversión válida si este escalón está sincronizado con el proceso de conversión. Si esta situación es asíncrona, la primera conversión no será válida y se requerirá de un tiempo de 1/fADC para que se produzca una

muestra correcta.

Rechazo 50 Hz/60 Hz (sinc

3)

La forma de conseguir el rechazo de la frecuencia es similar al del sinc4, variando el valor de FS. Sin embargo, en modo latencia cero, la frecuencia es un tercio. Por ejemplo, si con FS=96 conseguimos 50 Hz de frecuencia de salida con él deshabilitado, con él activo será de 16,7 Hz.

Gráfica 5. Respuesta del filtro sinc3 (FS=96).

Si FS=80, se consigue el rechazo a 60 Hz (por defecto, con modo latencia cero inactivo). Si está activo, la frecuencia es de 20 Hz.

Gráfica 6. Respuesta del filtro sinc3 con rechazo 50/60 Hz activo (FS=480).

De nuevo, si activamos el bit REJ60 con FS=96, se produce un notch de atenuación para 50 y 60 Hz. Esto supone una circunstancia similar a cuando se introduce esta opción para sinc4, y por lo tanto, trae consigo las mismas implicaciones (mayor ancho de banda pero peor rechazo a 50/60 Hz y peor atenuación a frecuencias superiores a las citadas).

Chop habilitado

Tenemos especial interés en esta configuración, puesto que el circuito integrado requiere de este modo cuando se alimenta la célula de carga con tensión alterna, puesto que los errores derivados por el offset en el ADC se minimizan. Además, el hecho de tenerlo activo supone un incremento de 0,5 bits en la resolución efectiva.

Aunque algunas características son independientes del estado del chopeo, otras sí que ofrecen diferencias.

Modo filtro SINC

4(chop habilitado)

La frecuencia de salida del ADC sigue la expresión:

𝑓𝐴𝐷𝐶 =

𝑓𝐶𝐿𝐾

4 · 1024 · 𝐹𝑆

Según esta expresión, el rango de frecuencias se encuentra entre 1,17 Hz y 1,2 kHz.

Figura 29. Esquema gráfico del ADC modo sinc4 con chop activado.

Esta configuración ofrece una reducción a la mitad del tiempo de establecimiento respecto al sinc4 con chop deshabilitado.

𝑡𝑒𝑠𝑡𝑎𝑏𝑙 𝑐𝑜𝑝 (𝑠𝑖𝑛𝑐 4)=

2 𝑓𝐴𝐷𝐶

Rechazo 50 Hz/60 Hz (sinc

4con chop habilitado)

La forma de conseguir este rechazo es similar al resto de regímenes de funcionamiento, a través de los bits de FS. Sin embargo, el comportamiento no es el mismo ya que el modo de chopeo introduce notches en múltiplos enteros impares de fADC/2. En la imagen, se muestra la

Gráfica 8. Respuesta del filtro sinc4 (FS=96) y chop habilitado.

Este rendimiento puede mejorar, como se ha expuesto previamente, habilitando el bit REJ60 del registro de modo.

Modo filtro SINC

3(chop habilitado)

En este modo, la frecuencia de salida de datos del ADC sigue la misma expresión que del filtro SINC3 sin chop activado y con modo latencia cero activado. Este modo es el más apropiado cuando trabajemos con frecuencias de salida de datos del ADC superiores a 320 Hz.

Figura 30. Esquema gráfico del ADC modo sinc3 con chop activado.

La frecuencia de salida de datos del ADC es la misma que para sinc3 sin modo latencia cero habilitado.

𝑓𝐴𝐷𝐶 =

𝑓𝐶𝐿𝐾

3 · 1024 · 𝐹𝑆

El tiempo de establecimiento es el mismo para ambos modos de filtro con chop habilitado.

𝑡𝑒𝑠𝑡𝑎𝑏𝑙 𝑐𝑜𝑝 (𝑠𝑖𝑛𝑐 3)=

2 𝑓𝐴𝐷𝐶

Rechazo 50 Hz/60 Hz (sinc

3con chop habilitado)

Su funcionamiento es similar al del sinc4 con chop habilitado, siendo su respuesta:

Si se activa el bit REJ60, mejora su respuesta.

Gráfica 11. Respuesta del filtro sinc3 (FS=96), REJ60=1 y chop habilitado.

3.2.3.5. Comparativa de modos del filtro digital

Como forma de resumen, el fabricante de la placa de evaluación AD7195 ofrece una tabla donde se recopilan los datos más relevantes que recoge cada tipo de configuración del filtro.

Aún así, la tabla del fabricante omite datos que son importantes, y que se recogen en las siguientes tablas:

Chop deshabilitado

fADC Rango fADC f3dB testablecimiento

Con Lat Cero Sin Lat Cero Con Lat Cero Sin Lat Cero

sinc4 𝑓𝐴𝐷𝐶 = 𝑓𝐶𝐿𝐾

4 · 1024 · 𝐹𝑆

𝑓𝐴𝐷𝐶= 𝑓𝐶𝐿𝐾

1024 · 𝐹𝑆

1,17Hz-1,2kHz

4,7Hz-4,8kHz

𝑓3𝑑𝐵

= 0,23 · 𝑓𝐴𝐷𝐶 𝑡𝑒𝑠𝑡𝑎𝑏𝑙 (𝑠𝑖𝑛𝑐 4)= 4 𝑓𝐴𝐷𝐶

sinc3 𝑓𝐴𝐷𝐶 = 𝑓𝐶𝐿𝐾

3 · 1024 · 𝐹𝑆

𝑓𝐴𝐷𝐶= 𝑓𝐶𝐿𝐾

1024 · 𝐹𝑆

1,56Hz-1,6kHz 4,7Hz-4,8kHz 𝑓3𝑑𝐵 = 0,272 · 𝑓𝐴𝐷𝐶

𝑡𝑒𝑠𝑡𝑎𝑏𝑙 (𝑠𝑖𝑛𝑐 3)=

3 𝑓𝐴𝐷𝐶

Tabla 3. Información del filtro del ADC con chop deshabilitado.

Chop habilitado

fADC Rango fADC f3dB testablecimiento sinc4 𝑓𝐴𝐷𝐶=

𝑓𝐶𝐿𝐾

4 · 1024 · 𝐹𝑆 1,17Hz-1,2kHz

𝑓3𝑑𝐵

= 0,24 · 𝑓𝐴𝐷𝐶 𝑡𝑒𝑠𝑡𝑎𝑏𝑙 (𝑠𝑖𝑛𝑐 4)= 2 𝑓𝐴𝐷𝐶

sinc3 𝑓𝐴𝐷𝐶= 𝑓𝐶𝐿𝐾

3 · 1024 · 𝐹𝑆 1,56Hz-1,6kHz

𝑓3𝑑𝐵

= 0,24 · 𝑓𝐴𝐷𝐶 𝑡𝑒𝑠𝑡𝑎𝑏𝑙 (𝑠𝑖𝑛𝑐 3)= 2 𝑓𝐴𝐷𝐶

Tabla 4. Información del filtro del ADC con chop habilitado.

3.2.3.6. Ruido en valor eficaz para distintas ganancias y frecuencia de

conversión

Ruido en valor eficaz respecto a ganancia y frecuencia (chop deshabilitado)

Tablas 5 y 6. Ruido en valor eficaz considerando ganancia y fADC para sinc3 y sinc 4 (chop off).

El valor de la palabra del filtro es el valor decimal del registro FS, que como hemos visto anteriormente, fija el valor de la frecuencia de los datos de salida.

Como resulta obvio, el tiempo de establecimiento es mayor cuanto menor sea la frecuencia (sistema más lento).

De esta comparativa se aprecia que el ruido en valor eficaz, expresado en nV, es ligeramente superior en modo sinc3 para cualquier valor de ganancia que tenga configurada la PGA. Sin embargo, ofrece un mejor tiempo de establecimiento para cualquier valor del valor decimal de los bits que componen FS.

Resolución efectiva respecto a ganancia y frecuencia (chop deshabilitado)

Cuando se habla de resolución, nos referimos a la mínima diferencia de tensión en la señal analógica de entrada, y que puede asegurar que va a producir una variación en el código digital de salida del ADC.