PROPOSTA DE UM MÓDULO PARA DESCRIÇÕES VERILOG NA FERRAMENTA FLEXMAP

Texto completo

(2) PROPOSTA DE UM MÓDULO PARA DESCRIÇÕES VERILOG NA FERRAMENTA FLEXMAP 1. INTRODUÇÃO Devido aos avanços tecnológicos na área de microeletrônica, tornou-se mais complexo a elaboração de um projeto de circuitos integrados (CIs). Um projeto de CI possui duas vertentes: circuitos analógicos e circuitos digitais. Um circuito analógico é efetuado a partir da análise de sinais de tensão e corrente, por outro lado, um circuito digital é construído considerando a funcionalidade lógica implementada. No mercado atual, há demandas constantes de equipamentos eletrônicos de melhor qualidade e esta demanda infere em um tempo de projeto mais curto. Por isso, na manipulação de um circuito digital é conveniente fazer o uso de ferramentas para automação, devido a grande quantidade de elementos lógicos que são manipulados na etapa de síntese versus as restrições consideradas como por exemplo, atraso e área. Desta forma, as ferramentas de Eletronic Design Automation (EDA) se tornam essenciais, visto que elas conseguem automatizar diversos processos do projeto, síntese e de simulação das descrições de um dado circuito digital. O processo da síntese de circuitos pode ser divido, tradicionalmente, em três etapas: a síntese de alto nível, a síntese lógica e a síntese física. A primeira síntese é responsável pela representação de mais alto nível do circuito, utilizando uma Linguagem de Descrição de Hardware (HDL, do inglês Hardware Description Language), como por exemplo, a linguagem Verilog (VHDL, 2012), para a descrição da lógica do circuito. Logo após, a etapa de síntese lógica é aplicada, nesta etapa é que ocorre o mapeamento tecnológico, cuja função é selecionar as portas lógicas, buscar redundâncias e aplicar as devidas simplificações. Por último, a síntese física recebe a descrição lógica da etapa anterior e gera uma estrutura do circuito, considerando a dimensão das portas, transistores e a geometria envolvida. O fato de ter várias linguagens para descrição de hardware dificulta procedimentos de assimilação entre as mesmas e se torna um obstáculo quando há necessidade de migração. Cada linguagem tem perfis diferentes, e isso dificulta a criação de ferramentas que possam contribuir amplamente em um projeto de circuitos digitais. A proposta desse trabalho é a criação de um módulo para aumentar o poder de reconhecimento de linguagens de descrição de hardware da ferramenta FlexMap (FlexMap, 2012). O FlexMap é uma ferramenta acadêmica de mapeamento que pretende criar um ambiente genérico e de rápida prototipação. O ambiente genérico é proposto para facilitar a comparação de diferentes metodologias e de diferentes nichos tecnológicos. Atualmente, este framework está limitado a apenas duas HDLs: AIG (do Inglês, And-Inverter-Graph) e EQN (do Inglês, Equation Format). Então, o módulo criado pretende expandir o poder computacional da ferramenta criando um algoritmo que reconheça uma descrição no formato Verilog. Este módulo permitirá carregar uma descrição de um dado circuito no formato Verilog e de acordo com os padrões da linguagem, será criada uma estrutura de.

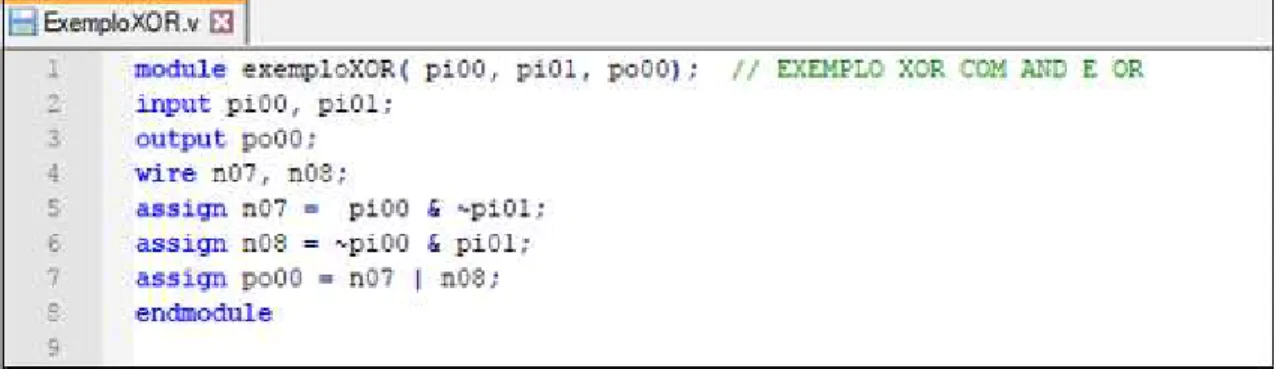

(3) dados para representar a lógica referente a este circuito. Basicamente, a estrutura da linguagem Verilog é constituída por uma listagem das entradas e saídas, declaração das variáveis do circuito e das definições das portas lógicas. No trecho que a estrutura externa de comunicação (listagens) é descrita, estão contidas as definições das entradas (inputs) e as saídas (outputs) do circuito, já nas declarações internas, estão descritos os elementos que formam a lógica do circuito em função das entradas. Assim, esse trecho contém as mesmas entradas e saídas devidamente tipadas, e também, a declaração dos fios de conexão (wires) intermediários do sistema. Na parte das definições, estão contidas quais são as saídas ou fios que recebem uma determinada lógica booleana entre as variáveis do sistema. 2. METODOLOGIA Antes mesmo de começar a implementação do módulo sobre o reconhecimento do padrão de Verilog, foi proposto uma análise sobre o FlexMap em busca de definir quais módulos seriam de interesse em ser produzidos para que esta ferramenta ampliasse suas funções dentro do mapeamento tecnológico de circuitos. Foi então, firmada a escolha de programar uma estrutura de dados que consiga carregar uma descrição de um circuito descrito em Verilog. Entretanto, como Verilog é uma linguagem que contém diversos tipos de operadores e podendo conter diversos blocos de controle, este trabalho foca apenas no carregamento de um benchmark específico da comunidade de síntese lógica disponibilizado pela Escola Politécnica Federal de Lausana (EPFL, 2017). Neste sentido, esse conjunto de circuitos apresenta uma menor complexidade de RSHUDGRUHV OyJLFRV FRQWHQGR DSHQDV RV RSHUDGRUHV GH $1'¶V H 25¶V 2XWUR PRWLYR pelo qual foi selecionado este benchmark, é porque ele possui alta compatibilidade com os formatos EQN e AIG, utilizados no FlexMap. A figura 1 apresenta a descrição da lógica booleana da porta lógica XOR entre as entradas primárias pi00 e pi01, em Verilog utilizando apenas as portas AND e OR e inversores.. Figura 1. XOR descrita em Verilog com portas ANDs e OR usando Notepad ++. Considerando que o framework FlexMap já possuía classes que faziam o arranjo dos nodos, foram efetuadas algumas extensões destas classes e de acordo com as necessidades da linguagem, foram efetuadas adequações. A figura 2 demonstra a ordem de execução do método parserVerilog que gera a estrutura que.

(4) representa a lógica descrita no formato Verilog. Todos as inserções em estruturas auxiliares serão utilizadas para mapear os nodos dentro da estrutura, podendo posteriormente favorecer à validação e manipulação da lógica da estrutura.. Figura 2. Fluxograma do método parserVerilog. A ideia proposta da estrutura é ter uma manipulação com facilidade dos dados, onde cada nodo tem as informações necessárias para conhecimento total de sua função dentro da estrutura. As informações serão utilizadas posteriormente para a migração e manipulação da lógica booleana. Tendo como exemplo a descrição utilizada na Figura 1, o método proposto obtém como resultado o grafo demonstrado na Figura 3. A Figura 3 ilustra o resultado da estrutura de dados proposta após o carregamento da descrição da Figura 1. Por serem circuitos combinacionais, os nodos intermediários são necessários para determinar os valores que estarão contidos nas saídas, e estes nodos intermediários serão dependentes das entradas do circuito.. Figura 3. Ilustração da estrutura gerada a partir do exemplo da Figura 1. Para a cerificação da competência do algoritmo são necessários testes, tanto na parte de revisão do código de escrita quanto na parte lógica do programa. Os testes foram efetuados no decorrer da programação, depois de programada uma funcionalidade do código, a mesma era testada e assimilada ao programa. Tornando assim, uma validação gradativa do processo de criação da estrutura de dados. Entretanto, ainda não há uma função que consiga verificar todas as etapas em um só conjunto. A contrapartida para este problema é uma possível assimilação.

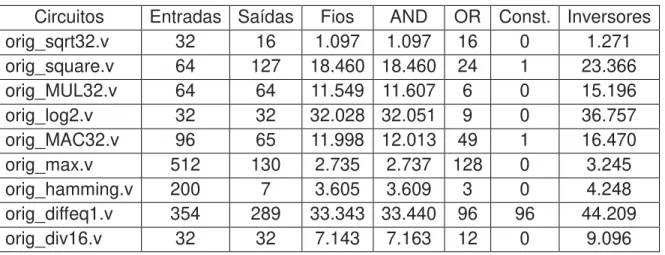

(5) automatizada entre duas estruturas do mesmo circuito, uma será a do FlexMap e a outra da ferramenta acadêmica de síntese e verificação lógica ABC (ABC, 2012). As duas descrições de saída serão comparadas e caso contenha total equivalência lógica, o circuito alvo na estrutura do FlexMap será considerado válido em todos aspectos. 3. RESULTADOS e DISCUSSÃO A validação manual do método realizou-se em uma comparação entre um procedimento que imprime a estrutura criada e o circuito em Verilog utilizado para gerar a estrutura. Por primeiro, foi comparada a parte das declarações das variáveis do circuito Verilog com as tabelas Hashs criadas no segundo passo da Figura 2. E em seguida, foi verificado as definições das portas, desta forma, nesta verificação, houve a comparação da linha que continha a palaYUD UHVHUYDGD ³assign´ GR 9HULORJ com a mesma variável desta porta que estava na estrutura, o objetivo desta etapa sucedeu-se em confrontar as entradas desta porta com as adjacências deste nodo da porta na estrutura. Na tabela 1, é exposto alguns dos circuitos utilizados na validação das variáveis do sistema com a quantidade de entradas, saídas, fios, portas, constantes e inversores. Tabela 1: Quantidades das variáveis do sistema, operadores lógicos, constantes e inversores dos circuitos utilizados nos testes. Circuitos Entradas Saídas Fios AND OR Const. Inversores orig_sqrt32.v 32 16 1.097 1.097 16 0 1.271 orig_square.v 64 127 18.460 18.460 24 1 23.366 orig_MUL32.v 64 64 11.549 11.607 6 0 15.196 orig_log2.v 32 32 32.028 32.051 9 0 36.757 orig_MAC32.v 96 65 11.998 12.013 49 1 16.470 orig_max.v 512 130 2.735 2.737 128 0 3.245 orig_hamming.v 200 7 3.605 3.609 3 0 4.248 orig_diffeq1.v 354 289 33.343 33.440 96 96 44.209 orig_div16.v 32 32 7.143 7.163 12 0 9.096 Após as análises manuais, nota-se que o módulo consegue manter a estrutura descrita, sem alterações. Foi muito importante para o início da programação ter considerado circuitos menos complexos em lógica booleana, o que resultou em menos exceções a serem consideradas. O FlexMap já possuía classes que faziam o arranjo dos circuitos, então, foram efetuadas algumas extensões destas classes de acordo com as necessidades da linguagem. Embora a ferramenta tenha métodos visuais para demonstração, os tamanhos dos circuitos alvos acabam inviabilizando tal ação. Já estão previstas adequações para reconhecimento de mais operadores e, também, de portas que recebem mais de duas entradas. Após a criação das novas classes para o reconhecimento dos operadores, será efetuado o procedimento de tradução da representação na estrutura em Verilog, para uma descrição no formato.

(6) EQN e AIG. Estes próximos passos serão necessários para que se amplifique a capacidade de reconhecimento de descrições a uma gama maior de circuitos. 4. CONSIDERAÇÕES FINAIS O módulo criado permite uma expansão no reconhecimento de HDLs para a ferramenta FlexMap, com este módulo a ferramenta consegue reconhecer um novo formato de descrição de circuitos digitais, e poderá também, realizar a manipulação da descrição Verilog para os formatos que ela já suporta, AIG e EQN. O FlexMap já possuía classes padrão para a estrutura, o que viabilizou mais facilmente a adequação ao formato Verilog. Os resultados demonstraram compatibilidade entre as descrições de circuitos utilizados e o resultado da estrutura gerada pelo método parserVerilog. Futuramente, com mais estudos a respeito da linguagem Verilog, espera-se obter maior adaptação a descrições de lógicas mais complexas por parte da ferramenta FlexMap. E para uma validação com maior confiabilidade, utilizar a ferramenta referência na área de síntese lógica denominada ABC. 5. REFERÊNCIAS ABC - BERKELEY, U. C. ABC: A System for Sequential Synthesis and Verification. [S.l.: s.n.], 2012. Online. Disponível em: <https://people.eecs.berkeley.edu/~alanmi/abc/>. Acesso em: 01 out. 2017. EPFL. École Polytechnique Fédérale de Lausanne. Lausanne: [s.n.], 2017. Online. Disponível em: <https://www.epfl.ch/index.en.html>. Acesso em: 30 set. 2017. GACI ± UFPEL. FlexMap: Uma Nova Abordagem para Mapeamento Tecnológico. Pelotas: [s.n], 2012. Online. Disponível em: <https://prezi.com/ejkhegevqvbt/flexmap-uma-nova-abordagem-para-mapeamentotecnologico/>. Acesso em 01 out. 2017. VHDL - Verilog Hardware Description Language. [S.l.: s.n.], 2012. Online. Disponível em: <http://www.verilog.com/index.html>. Acesso em: 01 out. 2017..

(7)

Figure

Documento similar

Criado Fernández, Ángela DIAZ BALADO, ALICIA Educación emocional como ferramenta para a prevención da violencia de xénero... ALUMNO/A TITOR/A TÍTULO

- Ahora sabemos más sobre cómo pueden empezar los conflictos, cuáles están en nuestras manos resolver y qué cosas podemos hacer para mejorar cuando los conflictos están en nuestras

Esta es la etapa principal de este módulo, ya que es la que lleva a cabo el paso de la señal en lógica TTL procedente de los módulos de cuenta de cada cilindro, a la señal de

En primer lloc, al parlar d'intel·ligència emocional, cal fer referència a Daniel Goleman (1995), ja que fou l'autor del best-seller que popularitzà aquest concepte. Partint

Educación Ambiental (Programa con Mención de Calidad Investigación en la enseñanza y el aprendizaje de las Ciencias, de la Universidad de Huelva). 3) En el campo de

-Módulo Deontología, Organización, Metodología y Turno de Oficio. -Módulo Jurisdicción Civil. -Módulo Jurisdicción Penal. -Módulo Asesoramiento Extrajudicial. -Módulo Extranjería

O obxectivo do blog é ser unha ferramenta de información de interese para os usuarios, de xeito que poida converterse nun vínculo

Sinalados con frechas, na parte dereita da pantalla aparece no Diario Oficial, coas publicacións máis recentes, e a ferramenta de busca por número de