UTILIZANDO A TÉCNICA OPERAND ISOLATION EM ARQUITETURAS VOLTADAS À CODIFICAÇÃO DE VÍDEO

Texto completo

(2) UTILIZANDO A TÉCNICA OPERAND ISOLATION EM ARQUITETURAS VOLTADAS À CODIFICAÇÃO DE VÍDEO 1. INTRODUÇÃO Com o crescente uso de aplicações e dispositivos eletrônicos que manipulam vídeos digitais em alta resolução, sendo estes utilizados em videoconferências, vídeos pela internet, etc., surge à necessidade de se aplicar um processo de compressão de vídeos a fim de reduzir o número de bits necessários para representar um vídeo digital (SILVEIRA, 2016). O padrão High Efficiency Video Coding (HEVC) é um dos mais novos padrões de compressão de vídeos, no qual foi projetado para satisfazer dois requisitos específicos: codificação de vídeos com alta resolução e o uso de arquiteturas de processamento paralelo (FONSECA, J.; SAMPAIO, M.,2014). O CABAC é um codificador de entropia do padrão HEVC. Ele é dividido em três principais sub-blocos, sendo eles: binarizador, modelador e Binary Arithmetic Encoder (BAE). O sub-bloco binarizador, tem a finalidade de mapear os elementos sintáticos para uma representação binária. As duas variáveis básicas do CABAC são o Range e o Low, que são atualizadas dependendo do tipo do bin, este que consiste no mapeamento de valores inteiros em uma sequência de bits que representa o valor original (RAMOS; ZATT; PORTO, BAMPI, 2016). Além da importância da compressão de vídeos, é necessário o estudo e a aplicação de técnicas visando baixo consumo de potência em dispositivos móveis, computadores, etc., a fim de buscar alternativas para que a bateria desses dispositivos tenha um tempo de durabilidade maior. A técnica estudada e aplicada neste trabalho refere-se à Operand Isolation, que consiste em bloquear a propagação dos sinais de entrada de um circuito quando a saída dele não for aproveitada (SASSI, 2013). Ela ocorre dentro do bloco combinacional em um circuito, isolando o circuito redundante, que possui ligação diretamente com operações redundantes contidas em um circuito e prevenindo a atividade de chaveamento (WALTER, 2011). Em síntese, torna-se de suma importância a pesquisa deste trabalho, no qual tem por objetivo analisar circuitos de multiplicação binária em termos de desempenho e porcentagem de redução no consumo de potência a partir da utilização da técnica de Operand Isolation. 2. METODOLOGIA Este estudo vislumbra, a partir de uma relevante pesquisa sobre o baixo consumo de potência dinâmica em circuitos digitais. Para isso se utilizaram duas arquiteturas que realizam multiplicações voltadas à área de codificação de vídeo. A operação dos Multiplicadores Binários possui duas entradas X e Y, em que X é um vetor fixo de nove bits e Y é um vetor que varia de dois a quatro bits, e o resultado da operação é armazenado num vetor Z. A entrada Y pode ser de dois a quatro bits, compondo as arquiteturas de 9x2 bits, 9x3 bits ou 9x4 bits, sendo estas configurações exigidas pelo padrão HEVC dentro do contexto do CABAC do padrão HEVC. A primeira fase caracterizou-se pelo levantamento de referencial teórico sobre o tema, em um segundo momento houve a implementação em VHDL da primeira.

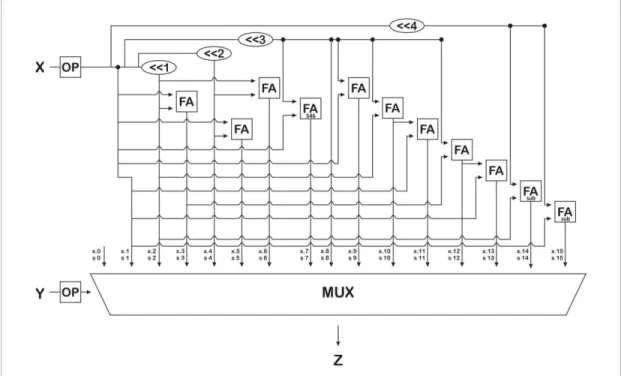

(3) arquitetura de multiplicação, denominada Somas Sucessivas e, posteriormente, da segunda arquitetura, chamada de Somas e Deslocamentos apresentada na (figura 01), ambas sem conter a técnica de Operand Isolation e logo após, contendo a referida técnica, sendo desenvolvido um testbench para emular o comportamento real do componente, através do software Modelsim.. Figura 1. Arquitetura Somas e Deslocamentos 9x4 bits com Operand Isolation descrito por Borges, T. (2017). Posteriormente, a fim de se obter valores reais das entradas X e Y e realizarse a validação, foi necessário utilizar o Software de Referência do padrão HEVC versão HM-16.6+SCM-5.1 através de uma máquina virtual com sistema operacional Linux. Com isso, foi efetuado um procedimento com os arquivos contendo sequência de vídeos padronizados para testes em hardware. Esse procedimento tinha a finalidade de transformar esses arquivos de uma maneira que o testbench pudesse fazer a leitura dos dados. Tendo-se todas as versões de 9x2, 9x3 e 9x4 bits das duas arquiteturas funcionais, partiu-se para a etapa de síntese e análise do consumo de potência dinâmica. Para isso, utilizou-se o ambiente de desenvolvimento da ferramenta Quartus II Web Edition da fabricante Altera ocorrendo à simulação da netlist através do testbench desenvolvido na etapa anterior, e isso gerou um arquivo de atividade de chaveamento do circuito, no qual possibilitou a análise do ganho de consumo de potência do circuito de cada uma das arquiteturas já mencionadas. A partir disso, foi realizada a coleta dos resultados através de tabelas, a fim de se realizar posteriores comparações com os ganhos obtidos a partir da aplicação da técnica de Operand Isolation em relação às versões arquiteturais sem conter a técnica mencionada, além de se realizar uma comparação entre as duas arquiteturas dos multiplicadores binários para se analisar qual de ambas se destacou como sendo a melhor arquitetura custo-benefício em relação à dissipação de potência dinâmica e desempenho..

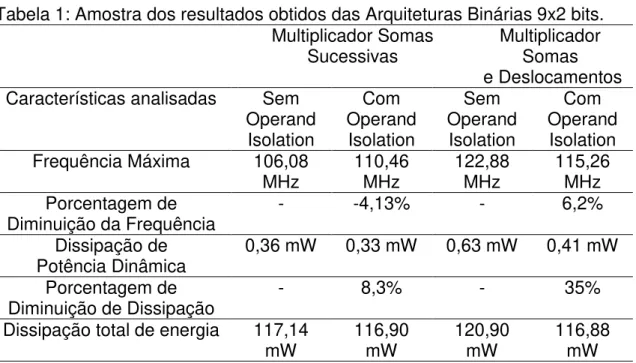

(4) 3. RESULTADOS e DISCUSSÃO Para a etapa de levantamento de resultados, utilizou-se o FPGA: Cyclone IV: EP4CE30F19A7. A análise de consumo de potência foi utilizada através de uma sequência de vídeo real denominada Kimono1_1920x1024_24.yuv, que é usada dentre outras por padrão para realizar testes de codificação de vídeo em hardware. O testbench foi projetado para rodar a 10.000 ns, para se obter 100 ciclos de clock na simulação análoga às versões 9x2, 9x3 e 9x4 bits das duas arquiteturas sem e com a técnica de Operand Isolation. A seguir serão apresentados, através das tabelas abaixo, os resultados obtidos de todas as versões das arquiteturas mencionadas, sendo elas 9x2, 9x3 e 9x4 bits: i). Tabela 1: apresentação da amostra dos resultados das arquiteturas de Somas Sucessivas e Somas e Deslocamentos versão 9x2 bits:. Tabela 1: Amostra dos resultados obtidos das Arquiteturas Binárias 9x2 bits. Multiplicador Somas Multiplicador Sucessivas Somas e Deslocamentos Características analisadas Sem Com Sem Com Operand Operand Operand Operand Isolation Isolation Isolation Isolation Frequência Máxima 106,08 110,46 122,88 115,26 MHz MHz MHz MHz Porcentagem de -4,13% 6,2% Diminuição da Frequência Dissipação de 0,36 mW 0,33 mW 0,63 mW 0,41 mW Potência Dinâmica Porcentagem de 8,3% 35% Diminuição de Dissipação Dissipação total de energia 117,14 116,90 120,90 116,88 mW mW mW mW Observa-se através da tabela 1 que ao se comparar as duas arquiteturas com e sem a técnica de Operand Isolation, que a arquitetura com 9x2 bits de Somas e Deslocamentos contendo a técnica mencionada apresenta um desempenho considerado bom e consome 35% menos de potência dinâmica no circuito, pois na Arquitetura do Multiplicador Somas Sucessivas como ocorreu um aumento na frequência, este resultado não era esperado conforme se buscou na literatura, porém (BRUCH, 2011), explica que no FPGA pode haver essa variação. ii). Tabela 2: apresentação da amostra dos resultados das arquiteturas de Somas Sucessivas e Somas e Deslocamentos versão 9x3 bits:. Tabela 2: Amostra dos resultados obtidos das Arquiteturas Binárias 9x3 bits. Multiplicador Somas Multiplicador Sucessivas Somas e Deslocamentos Características Sem Com Sem Com analisadas Operand Operand Operand Operand Isolation Isolation Isolation Isolation.

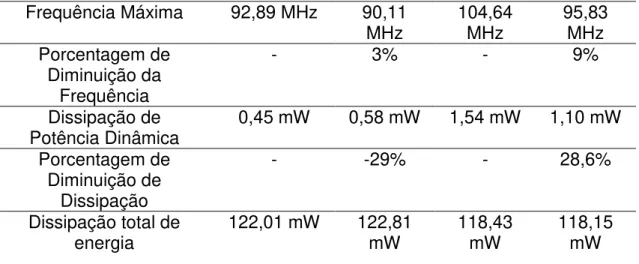

(5) Frequência Máxima. 92,89 MHz -. 90,11 MHz 3%. 104,64 MHz -. 95,83 MHz 9%. Porcentagem de Diminuição da Frequência Dissipação de Potência Dinâmica Porcentagem de Diminuição de Dissipação Dissipação total de energia. 0,45 mW. 0,58 mW. 1,54 mW. 1,10 mW. -. -29%. -. 28,6%. 122,01 mW. 122,81 mW. 118,43 mW. 118,15 mW. Nota-se na tabela 2 ao se comparar as duas arquiteturas com e sem a técnica de Operand Isolation, que a arquitetura 9x3 bits Somas e Deslocamentos contendo a técnica mencionada apresentam um desempenho bom e consome 28,6% menos de potência dinâmica no circuito. iii). Tabela 3: apresentação da amostra dos resultados das arquiteturas de Somas Sucessivas e Somas e Deslocamentos versão 9x4 bits:. Tabela 3: Amostra dos resultados obtidos das Arquiteturas Binárias 9x4 bits. Multiplicador Somas Multiplicador Sucessivas Somas e Deslocamentos Características Sem Com Sem Com analisadas Operand Operand Operand Operand Isolation Isolation Isolation Isolation Frequência Máxima 86,05 mW 81,45 90,49 89,82 MHz MHz MHz Porcentagem de 5,3% 0,7% Diminuição da Frequência Dissipação de 0,52 mW 0,54 mW 3,15 mW 1,97 mW Potência Dinâmica Porcentagem de -3,8% 37,5% Diminuição de Dissipação Dissipação total de 119,88 mW 120,05 121,34 118,33 energia mW mW mW. A partir da tabela 3, ao se comparar as duas arquiteturas com e sem a técnica de Operand Isolation, nota-se que a arquitetura 9x4 bits Somas e Deslocamentos contendo a técnica mencionada apresentam uma diminuição de desempenho quase não notável e consome 37,5% menos de potência dinâmica no circuito. Observa-se também uma variação em relação à Arquitetura de Somas e Deslocamentos sem a técnica de Operand Isolation, pois a síntese apresenta o valor de 3,15mW referentes à dissipação de potência dinâmica do circuito, enquanto que em relação à.

(6) dissipação total de energia apresenta o valor 121,34mW e esta grande diferença entre valores ocorre devido ao bloco da Arquitetura do Multiplicador de Somas e Deslocamentos ser muito pequeno em relação ao FPGA como um todo. 4. CONSIDERAÇÕES FINAIS O trabalho apresenta um estudo referente ao consumo energético em arquiteturas digitais voltadas à área de codificação de vídeo, possuindo circuitos puramente combinacionais e neles aplicou-se a técnica de Operand Isolation. Para esse estudo, foi necessário um levantamento teórico sobre o consumo de potência em dispositivos que manipulam vídeos digitais em alta resolução. Em vista disso, destacou-se como sendo a melhor arquitetura de custobenefício a Arquitetura do Multiplicador de Somas e Deslocamentos versão 9x2 bits contendo a técnica de Operand Isolation, esta que demonstrou uma queda de 6,2% em relação ao desempenho e uma redução de 35% no que se refere à dissipação de potência dinâmica, além de ser a mais simples em nível arquitetural, demonstrando assim ser a melhor dentre as demais, para ser utilizada na área de codificação de vídeo. 5. REFERÊNCIAS BRUCH, Jaison. Avaliação de alternativas arquiteturais para redução do consumo de energia na rede-em-chip socin. Dissertação (Trabalho de Conclusão de Graduação do Curso de Ciência da Computação), Universidade do Vale do Itajaí, Itajaí, 2011. FONSECA, J.; SAMPAIO, M. Padrão HEVC- Novas Tecnologias para Aplicações de Elevadas Taxas de Compressão de Vídeo. Revista de Tecnologia da Informação e Comunicação, v. 04, n. 02-08, p. 1-9, 2014. RAMOS, F; ZATT, B; PORTO, M; BAMPI,S. Low-Power Hardware Design for the HEVC Binary Arithmetic Encoder Targeting 8K Videos. In: Anais da IEEE Integrated Circuits and Systems Design (SBCCI); August 2016; Porto Alegre: University of Rio Grande of Sul. SASSI, A. Projeto de uma ULA de inteiros e de baixo consumo em tecnologia CMOS. Dissertação (Mestrado em Ciências, Programa de Engenharia Elétrica) Escola de Engenharia de São Carlos. Universidade de São Paulo, São Carlos, 2013. SILVEIRA, B. Exploração Arquitetural nas Métricas de Similaridade para Codificadores de Vídeo do Padrão HEVC. 69f. 2016. Dissertação (Mestrado em Engenharia Eletrônica e Computação), Universidade Católica de Pelotas, Pelotas, 2016. WALTER, F. Técnicas de Baixo Consumo para Módulos de Hardware de Codificação de Vídeo H.264. Dissertação (Mestrado em Microeletrônica). Universidade Federal do Rio Grande do Sul, Porto Alegre, 2011..

(7)

Figure

Documento similar

Durante a trajetória acadêmica, atua-se em áreas da Enfermagem voltadas à assistência-hospitalar, saúde pública, ensino e pesquisa, assim percebe-se que a

c) duas fotos 3x4 recentes, coloridas, com fundo branco;.. Esse valor é correspondente à emissão da primeira via da carteira, bem como na substituição ou renovação do

En el presente proyecto se estudiará la dinámica de poblaciones (tamaño y estructura poblacional) de las babosas Deroceras reticulatum, Milax gagates y Lehmannia marginata y de

rírse al interés que la Unión Soviética lia despertado en todos los sectores de la opinión británica desde que lucha con- tra Alemania, el autor contesta a la pri- mera

Referente à primeira pergunta da entrevista, pode-se dizer que houve uma preponderância de concepções associadas ao que há de mais recente em termos de teoria sobre

información, como una tendencia del informador hacia la recta averiguación y contrastación suficiente de los hechos y se aboga por la exigencia de un plus de diligencia al

é al nuestro Alcalde Entregador de las dichas nuestras Cañadas, é à sus Lugares-Thenientes; assi à los que agora son, como à los que seràn de aqui adelante, à quien esta

Los mercados zamoranos han estado más concurridos que el mes anterior, salvo en caballar y mular. Hubo pocas transacciones a precio ^ en baja, sobre todo en las especies de abasto.