Asimilación por ingeniería inversa del componente programable FPGA EP2C70F896C8 de la tarjeta PCI 811

103

0

0

Texto completo

(2) Universidad Central “Marta Abreu” de Las Villas Facultad de Ingeniería Eléctrica Departamento de Telecomunicaciones y Electrónica. TRABAJO DE DIPLOMA Asimilación por ingeniería inversa del componente programable FPGA EP2C70F896C8 de la tarjeta PCI 811 Autor: Mario Enrique Páez Ramos E-mail: mpaez@uclv.edu.cu Tutor: Dr. Juan Pablo Barrios Rodríguez E-mail: barrios@uclv.edu.cu Santa Clara 2013 “Año 55 de la Revolución”.

(3) Hago constar que el presente Trabajo de Diploma fue realizado en la Universidad Central “Marta Abreu” de Las Villas, como parte de la culminación de estudios de Ingeniería en Telecomunicaciones y Electrónica, autorizando a que el mismo sea utilizado por la Institución, para los fines que estime conveniente, tanto de forma parcial como total y que además no podrá ser presentado en eventos, ni publicados sin autorización de la Universidad.. ____________________ Firma del Autor Los abajo firmantes certificamos que el presente trabajo ha sido realizado según acuerdo de la dirección de nuestro centro y el mismo cumple con los requisitos que debe tener un trabajo de esta envergadura referido a la temática señalada.. ___________________. __________________. Firma del Autor. Firma del Tutor. _____________________. ________________________. Firma del Jefe de Departamento. Firma del Responsable de Información Científico-Técnica.

(4) i. PENSAMIENTO. “Hay una fuerza motriz más poderosa que el vapor, la electricidad y la energía atómica: la voluntad” Albert Einstein.

(5) ii. DEDICATORIA. A mis padres… A la motivación de mis hermanos Raquelita, Amanda y Luisi… A mi novia….

(6) iii. AGRADECIMIENTOS A mis padres por su incondicionalidad, por su esfuerzo para mi educación, porque siempre encuentro en ellos la seguridad y la confianza necesarias para enfrentar los mayores retos, por lo que soy, y lo que quiero ser. A mi abuelita querida por regalarme su tiempo, por la bien que se siente siempre ante sus ojos ser un héroe. Al Fidelon que fue como un padre para mí, por su servicialidad, por su paciencia en espera de las salidas para los Camilitos o para la Universidad pues siempre me cogía tarde, porque mucho antes de serlo me llamaba alegremente: Ingeniero! A mi abuelo Mario porque para su cuidado y su esmero he sido como el hijo varón que no tuvo, porque de chiquito orgulloso me paseó siempre a sus espaldas en la bicicleta. A mi tía Adis por su dulzura y por el provecho de sus reflexiones. A la ter nura de mis primas Amalia, Amanda, Amelia y Marialbis. A Yeilanis por su apoyo en la realización de este trabajo, por tantos momentos lindos que hemos vivido, porque siempre es un motivo y una invitación al amor. A mis eternos amigos, compinches de muchas alegrías y de mucho estudio, por todas las experiencias compartidas durante la universidad y antes de ella, resultado de etapas inolvidables en mi vida. A mi tutor que siempre encontró un espacio para atender mi trabajo, porque junto a sus certeras consultas y a la emoción emprendedora que me trasmitió logramos alcanzar los resultados finales de la investigación. A la supervisión del compañero Pierrat en el proyecto. A todos los profesores que han educado mi vocación estudiantil y mi conciencia. A la Liviii por todo su afecto, porque sé que siempre puedo contar con su amistad. A Lidennis por su atención, por esos almuerzos ricos de los domingos. Al cariño de Radis, Dolores y Mónica. A mi familia en sentido general. A todos, Gracias!.

(7) iv. TAREA TÉCNICA. 1. Estudio del funcionamiento de las tarjetas de expansión para la Interconexión de Dispositivos Periféricos (PCI). 2. Revisión bibliográfica acerca del diseño de aplicaciones PCI basadas en la capacidad de procesamiento de las FPGAs. 3. Contextualización del funcionamiento de la tarjeta 811 dentro del sistema general de la Estación de Vigilancia. 4. Documentación de la estrategia de diseño para FPGAs con el QuartusII. 5. Descripción de las especificaciones de funcionamiento de la tarjeta 811. 6. Documentación de la estructura modular del software desarrollado en el EP2C70F896C8 de la tarjeta 811. 7. Redacción del Informe Final.. Firma del Autor. Firma del Tutor.

(8) v. RESUMEN. La presencia de modernos componentes por la adquisición de tarjetas programables implementadas en una Estación de Vigilancia del espacio aéreo, sobre los cuales no se tiene más información que sus esquemas electrónicos y los códigos fuentes no documentados, impone la necesidad de la realización de este proyecto. Se pretende contribuir específicamente al desarrollo de documentación perteneciente a la T811, para la interconexión de dispositivos periféricos, que se encuentra insertada en un slot de la tarjeta madre de la computadora de control y se encarga de la interconexión con el resto de los componentes montados en la cabina de dirección de la Estación de Vigilancia. El cumplimiento de la meta planteada requiere de un estudio de la tecnología PCI y del dispositivo programable FPGA que controla su funcionalidad. Este dispositivo se encuentra configurado en VHDL, un lenguaje de descripción de hardware que facilitará la interpretación de la aplicación implementada; a partir de la caracterización de las señales de entrada y salida, de la realización de diagramas de flujo para detallar los procesos y de la creación de bloques funcionales para describir las etapas de escritura y de lectura pertenecientes al protocolo de comunicación del bus local PCI..

(9) vi. TABLA DE CONTENIDO PENSAMIENTO...................................................................................................................... i DEDICATORIA ..................................................................................................................... ii AGRADECIMIENTOS .......................................................................................................... iii TAREA TÉCNICA ................................................................................................................ iv RESUMEN ..............................................................................................................................v TABLA DE CONTENIDO .................................................................................................... vi INTRODUCCIÓN ...................................................................................................................9 Organización del Informe ....................................................................................................... 12 CAPÍTULO. 1.. ENTORNO. TECNOLÓGICO. PARA. LA. ASIMILACIÓN. DEL. FUNCIONAMIENTO DE LA T811 (PCI) ............................................................................. 13 1.1. Ingeniería Inversa ............................................................................................................ 13 1.1.1.. Ingeniería inversa del software, su definición .................................................... 14. 1.1.2. Beneficios de la ingeniería inversa del software ..................................................... 14 1.1.. Bus. Intercambio de información ................................................................................. 15 1.1.1.. 1.2.. Características generales de los buses ................................................................ 16. El bus local PCI ........................................................................................................... 17 1.3.1. Funcionalidad de los terminales PCI ...................................................................... 20 1.3.2. Secuencia de una transacción del bus PCI .............................................................. 24. 1.4. Conexión de una tarjeta PCI con un dispositivo FPGA ................................................... 26 1.4.1. Dispositivo programable FPGA ............................................................................. 27 1.5. Conclusiones del capítulo ................................................................................................ 29.

(10) vii. CAPÍTULO 2.. LA TARJETA 811 DENTRO DEL COMPLEJO DE DEFENSA.. CARACTERIZACIÓN .......................................................................................................... 31 2.1. La electrónica implementada en el sistema de defensa antiaéreo ...................................... 31 2.2. Tarjeta 811 para la interconexión de componentes periféricos .......................................... 33 2.2.1. Modo de comunicación empleado en las tarjetas programadas ............................... 34 2.3. Características del dispositivo FPGA EP2C70F896C8 ..................................................... 37 2.3.1. Facilidades para el análisis del funcionamiento con el Quartus II ........................... 38 2.3.2. Implementación del componente programable con VHDL ..................................... 39 2.3.2.1. Estructura del lenguaje VHDL. Generalidades .................................................... 40 2.3.2.2. Diagramas de Estados. Máquinas de Estado Algorítmicas (ASM) ....................... 42 2.4 Conclusiones del capítulo ............................................................................................... 44 CAPÍTULO 3. ASIMILACIÓN DE LA FUCIONALIDAD DEL CÓDIGO FUENTE DE LA T811....................................................................................................................................... 45 3.1. Arquitectura del diseño. Mecanismos de funcionamiento empleados ............................... 45 3.1.1. Declaraciones de los componentes. Descripción estructural de hardware ............... 47 3.1.2. Procesos que se encargan de la disponibilidad y activación de los componentes..... 51 3.2. Procesos en la PCI que definen el direccionamiento, el control y la transferencia de datos53 3.2.1. Secuencia que rige el protocolo de comunicación entre los agentes PCI ................. 55 3.2.2. Secuencia que rige el acceso al bus local PCI durante etapas de configuración, de control o de datos ............................................................................................................ 58 3.3. Estructura del diagrama funcional del Bus Local PCI ...................................................... 62 3.4. Conclusiones del Capítulo ............................................................................................... 65 CONCLUSIONES ................................................................................................................. 66 RECOMENDACIONES ........................................................................................................ 67 ABREVIATURAS Y ACRÓNIMOS ..................................................................................... 68.

(11) viii. REFERENCIAS BIBLIOGRÁFICAS .................................................................................... 70 ANEXOS ............................................................................................................................... 73 A.1. Códigos de los comandos PCI. Puerto C_BE_n(4..0) ...................................................... 73 A.2. Asignación de los conectores .......................................................................................... 76 A.3. Descripción básica del Quartus II .................................................................................... 78 A.4. Bloques de escritura y lectura durante una etapa de configuración .................................. 81 A.5. Bloques de escritura y lectura durante una etapa de control de E/S .................................. 82 A.6. Código fuente de la tarjeta 811. PCI ................................................................................ 82 A.7. Correspondencia de los terminales PCI con los pines en el dispositivo FPGA ............... 100.

(12) INTRODUCCIÓN La alta disponibilidad combativa de nuestros medios para la defensa y la existencia de un sistema competente con la capacidad de responder al enemigo, y a la magnitud de sus fuerzas, siempre ha sido de gran importancia por cuanto representa conservar la Paz. A partir del año 1963, tras la primera visita del Comandante en Jefe Fidel Castro Ruz a la Unión de Repúblicas Socialistas Soviéticas (URSS), con motivo de elevar la potencialidad defensiva de la República de Cuba se realizaron una serie de acuerdos con el Gobierno de la URSS, a través de los cuales se recibió suficiente técnica combativa, armamento y materiales de guerra fomentando una considerable ayuda en la elevación del equipamiento técnico de las Fuerzas Armadas Revolucionarias. Constituía un reto asumir esa cantidad y diversidad de armamento, pues las FAR cubanas de entonces no poseían esa cantidad de personal con el nivel de preparación general indicado. Debido a esta circunstancia, el 13 de marzo de 1963, al intervenir en la escalinata de la Universidad de La Habana, en el acto conmemorativo del Sexto Aniversario del Asalto al Palacio, el Comandante en Jefe Fidel Castro planteaba: “Ahora estamos reclutando el personal para nuestras armas más modernas. Y necesitamos técnicos, necesitamos estudiantes de la Facultad de Tecnología, necesitamos personal con alto nivel. Y hemos acordado seleccionarlo primero en las Fuerzas Armadas, después en los centros de trabajo (…) En último término algunos estudiantes, dado que necesitamos personal con un elevado nivel de cultura y conocimientos técnicos que podrán aprender a utilizar las armas modernas que están a nuestra disposición…¨ Así se desarrolló en todo el país el proceso de selección del personal que pasaría a asimilar la nueva técnica militar, cumpliendo siempre los principios de voluntariedad e incondicionalidad a la Revolución. (Gómez, 2013) Hoy es una tarea de gran impacto la modernización de los sistemas de combate en nuestro país, pues el desarrollo actual de las tecnologías de la información y la comunicación (TICs) se ha puesto en función de la industria militar y constituye un deber para el estado cubano llevar a cabo esta labor renovadora. Con motivo del análisis de la electrónica digital implementada en una Estación de Vigilancia del espacio aéreo, a partir de la adquisición de varias tarjetas diseñadas con electrónica digital programada, de las cuales hay que obtener su funcionalidad, surge la necesidad de realizar un trabajo de documentación descriptiva, donde queden planteadas las principales características y el modo de operación de la nueva tecnología adquirida. Será puesto en marcha por la Facultad.

(13) de Ingeniería Eléctrica de la Universidad Central “Marta Abreu” de las Villas con el apoyo de la entidad CID-3 de la Unión de Industrias Militares. El proceso de realizar nuevos algoritmos a partir de la experiencia y el conocimiento que se tiene sobre el funcionamiento de la Estación, aunque se cuenta con suficiente personal preparado resultaría un trabajo de mayor envergadura, pues no existe experiencia alguna sobre el tratamiento digital y programado que se debe realizar para implementar los algoritmos planteados. La experiencia obtenida por especialistas extranjeros ha permitido conocer que un proceso de este tipo requiere de un personal calificado en la teoría de funcionamiento de la Estación dada y que además tenga suficiente preparación en los temas de la electrónica digital y de la electrónica digital programada. Un grupo con estas características necesitaría un tiempo de trabajo que puede oscilar entre los 12 y 15 años para evaluar las partes de la Estación analógica que se convertirían en procesos digitales, realizar la conversión funcional teórica de integradores, discriminadores, esquemas de análisis, filtros de seguimiento, sistemas a lazo cerrado, entre otros; para conformar también el diseño de los algoritmos de trabajo de la estación por partes o sistemas independientes, simularlos y compatibilizarlos entre sí, programarlos para diversos componentes, llevar a cabo la creación de los esquemas electrónicos y las tarjetas de circuitos impresos, la realización del montaje de las placas, el cableado entre las mismas y por último las pruebas funcionales a la nueva estación que estaría surgiendo, implicando así una transformación realmente compleja (Pierrat, 2013a). La otra alternativa para resolver el problema planteado es mediante la vía científica, aprovechando la oportunidad única de tener el esquema electrónico y los códigos fuentes no comentados que están en los componentes programables de las tarjetas y conociendo además, las señales de entrada y salida presentes en sus conectores, es posible, mediante la ingeniería inversa al hardware programado, obtener la funcionalidad de la tarjeta instrumentada en la Estación de Vigilancia del espacio aéreo. En el transcurso de la Segunda Guerra Mundial, nace la ingeniería inversa, cuando los ejércitos enemigos incautaban insumos de guerra como aviones u otra maquinaria de guerra para mejorar las suyas mediante un exhaustivo análisis. La situación de estudio es un caso particular de análisis y rediseño, que se fundamenta en diversos aspectos del producto original y es necesaria su ejecución pues el proceso de diseño y la documentación original no están disponibles (López, 2010). Esta tecnología está basada en la electrónica programada sobre circuitos impresos de cuatro capas y actualmente se encuentra funcionando en la técnica de combate. Es imprescindible prever la posibilidad de averías o errores que provoquen un incorrecto funcionamiento en el.

(14) complejo de defensa. La realización de este proyecto brindará información vinculada con la implementación de un hardware de gran complejidad y valor del cual no se tiene dominio: la tarjeta 811(PCI) que es controlada por el componente programable FPGA EP2C70F896C8. Esta investigación se enfocará principalmente en descifrar la interrogante que a continuación se expone: ¿Cómo realizar la labor de asimilación de tecnología y obtención del funcionamiento del componente programable FPGA EP2C70F896C8 de la tarjeta 811(PCI) mediante la ingeniería inversa? El propósito global del estudio y objetivo general de la investigación es: Documentar la funcionalidad del componente programable FPGA EP2C70F896C8 de la tarjeta 811(PCI). Dando origen a los objetivos específicos que indican lo que se pretende realizar en cada una de las etapas de la investigación sirviendo de guía al estudio, los cueles son: 1. Investigar acerca del funcionamiento de las tarjetas de expansión para la Interconexión de Dispositivos Periféricos. 2. Estudiar aspectos relacionados con del diseño de aplicaciones PCI basadas en la capacidad de procesamiento de las FPGAs. 3. Contextualizar el funcionamiento de la tarjeta 811(PCI) dentro del sistema general de la estación de vigilancia. 4. Analizar la estrategia de diseño para circuitos FPGA con el QuartusII. 5. Describir las especificaciones de funcionamiento de la tarjeta 811(PCI). 6. Conformar la estructura modular del software desarrollado en el EP2C70F896C8 de la tarjeta 811(PCI)..

(15) Organización del Informe En el CAPÍTULO 1 se describen los principales aspectos relacionados con la naturaleza de las señales que se intercambian durante el protocolo de comunicación del bus local PCI. El CAPÍTULO 2 caracteriza la tarjeta PCI, a partir del dispositivo FPGA EP2C70F896C8, dentro del complejo de defensa perteneciente a la estación de vigilancia. Por su parte el CAPITULO 3 se dedica exponer la secuencia lógica que rige el funcionamiento del bus local PCI empleando para ello herramientas gráficas que ilustran el intercambio de información. Posteriormente aparecen las Conclusiones y Recomendaciones, y las Referencias Bibliográficas. Se incluyen además los Anexos para complementar la visión que se quiere dar acerca de los diferentes temas tratados a lo largo del trabajo..

(16) CAPÍTULO 1. ENTORNO TECNOLÓGICO PARA LA ASIMILACIÓN DEL FUNCIONAMIENTO DE LA T811 (PCI). La nueva tecnología recibida deberá ser sometida a un estudio detallado, hasta el punto que se pueda entender, modificar y mejorar su funcionamiento, teniendo en cuenta los intereses de la Estación de vigilancia. A este proceso cuyo principal objetivo es obtener información de la tarjeta 811 (PCI) se le conoce como Ingeniería Inversa, así denominado por avanzar en dirección opuesta a las tareas habituales de ingeniería, que consisten en utilizar datos técnicos con la meta de elaborar un producto determinado (Quintero et al., 2012). Para facilitar el trabajo se abordarán en este capítulo el modo a proceder y los principales rasgos de la tecnología del hardware mencionado. 1.1. Ingeniería Inversa La mayor parte de la ingeniería en el mundo es generada por los países más desarrollados que se mantienen a la vanguardia en tecnología y en filosofías de producción. Esto crea un fenómeno de desigualdad tecnológica a nivel mundial, que se agudiza debido a la inmensa diferencia en calidad y cantidad de recursos que son destinados a las instituciones dedicadas a la investigación y al desarrollo en estos países, en comparación con aquellos que se enfocan sobre todo en formar técnicos como es el caso de las naciones en vías de desarrollo. Ante este panorama, se buscan alternativas para aprovechar y reutilizar todos los conocimientos existentes sobre la forma de crear productos. Las fórmulas ingenieriles certificadas cobran importancia especial frente a la feroz competencia de estos tiempos. La ingeniería tradicional parte de un conjunto de especificaciones técnicas que contienen información sobre la funcionalidad de la mercancía, el cumplimiento de normas, la sustentabilidad ambiental y la viabilidad económica, entre otras, para plantear su adecuada fabricación y así llegar a un artículo físico. Como se podrá adivinar, se requiere de un considerable tiempo de estudio de mercado, diseño del producto y del proceso de producción, modelado, pruebas de factibilidad, funcionalidad y conformabilidad, estudio de materias primas, evaluaciones de costos y tiempos, etcétera. Es un procedimiento ineludible para la obtención de piezas originales(Morales, 2013). Una vez que una mercancía ha sido probada con éxito, lo obvio es fabricarla hasta que su ciclo en el mercado termine. Lo anterior suena lógico para el creador, pero ¿qué sucede con la competencia?, ¿cómo fabricar algo de lo cual no se tiene información original?, ¿cómo recuperar el tiempo de ventaja que llevan los desarrolladores?, ¿cómo obtener mediciones cuando no existen patrones ni instrumentos para extraer la información?, ¿cómo invertir los.

(17) recursos en una investigación y desarrollo que, en el mejor de los casos, lleva a obtener un artículo similar al que ya está en el mercado? y ¿cómo realizar un estudio ingenieril cuando no se cuenta con los suficientes recursos humanos, económicos y/o tecnológicos? Existe una respuesta real, factible y legal a estas preguntas. La Ingeniería Inversa plantea el camino desde el extremo final del ciclo, es posible llegar de la parte física a la información ingenieril para de nuevo regresar a ella con nuevos provechos. 1.1.1. Ingeniería inversa del software, su definición La Ingeniería Inversa es un proceso analítico-sintético que busca determinar las características y/o funciones de un sistema, una máquina, un producto, una parte de un componente o un subsistema con el propósito de determinar un modelo genérico (López, 2010). Se puede definir además como el proceso de transformación de código en un modelo a través de una correspondencia con un lenguaje de implementación específico. Analizar un sistema determinado tiene dos objetivos: Identificar los componentes de un sistema y sus interrelaciones Crear representaciones de un sistema en otra forma de abstracción más alta Cómo no debe utilizarse la ingeniería inversa en el software En la actualidad existe una concepción errónea sobre la ingeniería inversa del software, generalmente se la asocia con el hecho de ruptura de seguridades que protegen los derechos de propiedad intelectual con fines bajos como la piratería y la manipulación del código programable para uso indebido de la información contenida. Cómo debe utilizarse la ingeniería inversa en el software La investigación muestra el surgimiento de la ingeniería inversa del software como una técnica necesaria para reducir los altos costos de mantener un producto software (detallado anteriormente). El proceso de entender cómo fue conceptuado un producto software requiere un bagaje de conocimientos mayores que el proceso en sí de desarrollar dicho producto, por lo tanto la necesidad de investigar los procedimientos de fabricarlo descansan necesariamente en una metodología de desarrollo de software. 1.1.2. Beneficios de la ingeniería inversa del software Utilizar ingeniería inversa en el software promueve grandes beneficios: Permite optimizar un código programable de un sistema software heredado para acoplarlo a las nuevas necesidades del usuario..

(18) Permite documentar un producto software para su mejor entendimiento cuando no existe información técnica al respecto. Permite entender cómo fue diseñado un producto software, con la ausencia de sus mentores, reduciendo el costo aplicado a su mantenimiento. Permite mejorar las aptitudes de analista y diseñador de software. Permite realizar la portabilidad de un producto software importante a nuevas arquitecturas. Permite optimizar los recursos software disgregados en un entorno, englobándolos en un nuevo producto con mejores características(Morales, 2013). Permite reducir el índice de errores de un producto por medio de antipatrones. 1.1. Bus. Intercambio de información El "bus" es una palabra que traducida literalmente significa transporte. Las distintas unidades funcionales de una computadora necesitan comunicarse, por lo tanto deben existir líneas que transmitan señales con funciones específicas para interconectar estos módulos (CPU, Memoria, E/S), siendo el Bus el elemento fundamental. Es un canal de comunicación compartido que utiliza un conjunto de entre 50 y 100 líneas para conectar múltiples subsistemas, cada cable o línea eléctrica transmite un único bit de información, “0” (cero voltios) o un “1” (más de cero voltios), en un determinado momento (Tanenbaum and Seone, 1985). Por tanto de acuerdo a ciertas reglas o normas de conexión el elemento que permite transferir toda la información es el Bus, desde las operaciones más sencillas de la Unidad Central de Procesamiento, hasta la transferencia de datos entre los distintos dispositivos conectados al sistema central como son memorias, tarjetas gráficas, teclados y otros periféricos o dispositivos del ordenador. Desempeña además las tareas de enlace y de conmutador pues permite en cada momento seleccionar los dispositivos que se comunican a través suyo. En las transferencias de información que se realizan en los buses, existen dos agentes involucrados: el que origina la transferencia, denominado maestro de la transferencia y el que responde a la misma, denominado esclavo de la transferencia. La operación básica del bus se denomina ciclo de bus. Un ciclo permite realizar una transferencia elemental de un dato entre dos dispositivos. En esta transferencia, la información se lleva de un elemento que se denomina fuente a otro que se denomina destino. Los buses modernos permiten agrupar varias transferencias en una sola operación, conocida como transacción, estas pueden tener los mismos o distintos destinos, o incluso un mismo elemento puede actuar como fuente y como destino en distintas transferencias de una misma transacción..

(19) 1.1.1. Características generales de los buses Un bus puede ser paralelo, multiplexado o serie. El bus paralelo tiene un ancho de palabra que coincide con el ancho de la información a transmitir. (PCI) El bus multiplexado se originó como consecuencia de tener que ahorrar conexiones (pines) debido a la necesidad de una alta integración de los componentes del ordenador. Un ejemplo de este uso es comunicar las direcciones de memoria entre el microprocesador y la memoria (en su forma física de chips). Consiste en utilizar los mismos hilos para enviar en momentos distintos informaciones distintas, permitiendo con el uso de señales adicionales identificar la información que circula por el bus en cada momento. Generalmente el resto del sistema exige que el bus no esté multiplexado. En estos casos en los extremos del bus se encontrarán multiplexores para realizar la multiplexación/demultiplexación. El bus serie está formado únicamente por un par de hilos, por los que circula la información bit a bit. Durante el envío es necesario dividir la palabra en bits así como realizar un agrupamiento de estos bits para formar una palabra en la recepción. (USB) En relación a la función que realizan los buses puede ser de carácter general o específico. Los buses específicos, dedicados cada uno a una función permiten un diseño sencillo, y que la capacidad de transferencia total sea mayor. Los buses de carácter general reducen el número de hilos que llegan a la CPU, por lo que son especialmente útil para microprocesadores. El esquema formado por estos buses es comparativamente más sencillo, aunque cada bus individualmente sean más complejos que los de carácter global (Mano, 1994). Señales que constituyen un bus Existen varios tipos de bus, pues cada dispositivo necesita enviar diferentes tipos de información. Las líneas o señales de un bus se pueden clasificar en tres grupos funcionales: líneas de direcciones (de memoria o E/S), de datos y de control. Líneas/bus de datos: Camino para transferir datos entre los módulos del sistema. Su anchura (número de líneas eléctricas) suele ser una potencia de dos, 8, 16, 32, determinando cuántos bits se pueden transmitir simultáneamente, factor clave a la hora de determinar las prestaciones del sistema..

(20) Figura 1.1 Señales que componen un Bus Líneas/bus de direcciones: Direcciona la fuente o el destino de los datos, se encarga de determinar en qué lugar exacto de memoria se escribirá el dato. Su anchura determina la cantidad máxima de memoria direccionable en el sistema. Líneas/bus de control: Gestiona el acceso y el uso de las líneas de datos y de dirección, señalizando peticiones y reconocimientos e indicando que tipo de información pasa por las líneas de datos. Maneja el momento y la forma de escribir el dato. Jerarquía de buses Es preciso que entre los buses exista un cierto rango o prioridad para evitar una serie de problemas fundamentales que se enfrentan al conectar un gran número de dispositivos, como son: La diferencia de velocidad de los dispositivos que afecta negativamente al rendimiento global, pues mientras los dispositivos lentos realizan una única transferencia, otro dispositivo más rápido podría haber realizado muchas más. La posibilidad de actuar los buses como “cuello de botella” en dependencia de la demanda de transferencia, si es mayor que la capacidad del bus, los dispositivos deberán entonces esperar mucho tiempo para poder transmitir. La existencia de un mayor retardo de propagación, pues el bus ha de tener mayor longitud para poder soportar un mayor número de dispositivos (Abel, 1996). 1.2. El bus local PCI El bus local PCI, por sus siglas en inglés Peripheral Component Interconnect, (Interconexión de Componentes Periféricos) es un bus de altas prestaciones que trabaja con líneas de dirección y de datos, multiplexadas con longitudes de 32 y 64 bits. Su uso se orienta como mecanismo de interconexión entre controladores de periféricos altamente integrados, como son las placas de expansión y los sistemas procesador/memoria. Acercando las funciones periféricas con.

(21) mayores requerimientos de ancho de banda al bus del microprocesador del sistema, se puede eliminar el atascamiento que se crea entre el procesador y sus periféricos. Cuando un diseño tipo “Local Bus” es utilizado, pueden obtenerse ganancias sustanciales en cuanto a rendimiento con interfaces gráficas para el usuario (GUIs, Graphical User Interfaces) y otras funciones de gran ancho de banda.(Group, n.d.) El líder de la creación de este nuevo grupo de trabajo fue Intel, corporación pionera en la fabricación de circuitos integrados, superando las debilidades de arquitecturas de buses anteriores como VESA, ISA y EISA. Los componentes e interfaces agregables PCI son independientes del tipo de microprocesador, permitiendo una eficiente transición a futuras generaciones de procesadores y al uso de arquitecturas multiprocesador. Esta independencia permite que el bus local PCI sea optimizado para funciones E/S, habilita la operación concurrente del bus local con el subsistema procesador/memoria y acomoda múltiples periféricos de altas prestaciones conjuntamente con el incremento de gráficos en la definición de la imagen ( LAN, SCSI, FDDI, HDD, etc)(Mueller, 2011). PCI rediseñó el bus tradicional de la PC insertando nuevas conexiones (puentes) para el intercambio de información entre la CPU y las interfaces de E/S. En vez de un apoyo ligero que actúa directamente sobre el bus del procesador, un nuevo conjunto de dispositivos para dar extensión al bus, figura 1.3, fue desarrollado. Los sistemas que integran el bus PCI se pusieron disponibles a mediados de 1993 y desde entonces se han convertido en un soporte principal para las PC.. Figura 1.2 Arquitectura típica del bus local PCI.

(22) Se puede observar en la figura 1.2 que el sistema procesador/cache/memoria se encuentra conectado al bus PCI a través de un “Puente PCI” (Mueller, 2011). Este puente provee de un camino de bajo retardo y gran ancho de banda, por el cual el procesador puede acceder a cualquier dispositivo mapeado en memoria o en los espacios para I/O y permite que cualquier Master PCI tenga acceso directo a memoria. El puente puede, opcionalmente, incluir funciones almacenamiento y designación (buffering / posting) y funciones centrales PCI como el arbitraje. Conectores PCI Por lo general, las placas madre cuentan con al menos 3 ó 4 conectores PCI, identificables generalmente por su color blanco estándar. La interfaz PCI de 32 bits tiene un conector de 124 pasadores, anexo A.2. También existen dos niveles de señalización de voltaje: 3,3 V para los ordenadores portátiles 5 V para los equipos de escritorio El voltaje señalizado no es igual al voltaje de la fuente de alimentación de la placa madre, sino que es el umbral de voltaje necesario para el cifrado digital de los datos. Como se puede observar en la figuras 1.3 y 1.4, existen dos tipos de conectores de 32 bits.. Figura 1.3 Conector PCI de 32 bits, 5 V. Figura 1.4 Conector PCI de 32 bits, 3.3 V Interoperabilidad Generalmente no se pueden cometer errores al introducir una tarjeta PCI en una ranura PCI. Si la tarjeta encaja correctamente, entonces es compatible. De lo contrario, existen mecanismos infalibles que pueden evitar dicha instalación, como se muestra en la figura 1.5.Existen tarjetas de expansión equipadas con lo que se denomina conectores "universales", es decir, que poseen dos tipos de dispositivos infalibles (dos muescas). Dichas tarjetas de expansión pueden detectar el voltaje señalizado y adaptarse a él. Por lo tanto, pueden insertarse tanto en ranuras de 3,3 V como en ranuras de 5V (Dembowski, 2003)..

(23) Figura 1.5 Inserción del dispositivo PCI sobre el Slot de la PC 1.3.1. Funcionalidad de los terminales PCI El bus PCI es un bus multiplexado que utiliza los mismos hilos para direcciones y para datos. Consta de 49 líneas de señales obligatorias, las cuales se dividen en los siguientes grupos que definen su funcionalidad: Terminales (líneas) de Sistema: Constituidas por los terminales de reloj y de inicio (reset). Terminales de Direcciones y Datos: Incluye 32 líneas para datos y direcciones multiplexadas en el tiempo. Las otras líneas del grupo se utilizan para interpretar y validar las líneas de señal correspondientes a los datos y a las direcciones. Terminales de Control de la Interfaz: Controlan la temporización de las transferencias y proporcionan coordinación entre los que las inician y los destinatarios. Terminales de Arbitraje: A diferencia de las otras líneas de señal del PCI, estas no son líneas compartidas. Cada maestro del PCI tiene su par propio de líneas que lo conectan directamente al árbitro del bus PCI. Terminales para Señales de Error: Utilizadas para indicar errores de paridad, u otros. Terminales de Interrupción: Para los dispositivos PCI que deben generar peticiones de servicio. Igual que los terminales de arbitraje, no son líneas compartidas sino que cada dispositivo PCI tiene su propia línea de petición de interrupción a un controlador de interrupciones. Terminales de Soporte de Cache: Estos terminales permiten el uso de memorias cache en el bus PCI asociadas a un procesador o a otro dispositivo. Terminales de Extensión a Bus de 64 bits: Incluye 32 líneas multiplexadas en el tiempo para direcciones y datos y se combinan con las líneas obligatorias de dirección y datos para constituir un bus de direcciones y datos de 64 bits. Hay otras líneas de este grupo que se utilizan para interpretar y validar las líneas de datos y direcciones. Por último, hay dos líneas que permiten que dos dispositivos PCI se pongan de acuerdo para usar los 64 bits..

(24) Terminales de Test (JTAG/Boundary Scan): Estas señales se ajustan al estándar IEEE 1149.1 utilizado para testear circuitos impresos a través de un escaneo de límites. Los grupos funcionales genéricos de una PCI son expuestos en la figura 1.6, a la derecha se encuentran las señales obligatorias y a la izquierda las opcionales. Las líneas que tienen un # al final del nombre son aquellas que son activas en nivel bajo. Los sentidos de las flechas son para un dispositivo que controle la tarjeta (master-target). Las líneas pueden ser de distintos tipos, las de entrada son estándar, mientras que las salidas son: Tri-Estado: Además de los valores convencionales alto ´1´ y bajo ´0´, permite la condición de alta impedancia ´Z´, cuando está activada (enabled=1) actúa como un circuito abierto impidiendo el paso de la señal). Tri-Estado Sostenido: Puede ser activada para el intercambio únicamente por un dispositivo a la vez, establece una conexión ininterrumpida en cada momento. Drenador Abierto: Permite que varios dispositivos compartan la conexión como en una compuerta lógica OR cableada. Líneas de Sistema CLK: Señal de Entrada. Provee la temporización para todas las transacciones del dispositivo y es muestreada en el flanco ascendente. Se pueden utilizar frecuencias de reloj de hasta 33 MHz, para 32 bits. RST#: Señal de Entrada. Se utilizada para llevar todos los registros, secuenciadores y señales específicas del dispositivo PCI a su estado inicial. Líneas de Direcciones y Datos AD [31::00]: Señales Tri-Estado. Multiplexan sobre las mismas líneas el flujo de direcciones y datos. Una transferencia de datos se lleva a cabo cuando IRDY# y TRDY# están ambas activas. C/BE [3::0] #: Señales Tri-Estado. Multiplexadas con órdenes del bus (Command Bus) y de byte activo (Byte Enable). Durante la fase de direccionamiento de una transacción estas líneas definen el comando del bus. Durante la fase de datos se usan como habilitaciones, indicando cuál de los cuatro grupos de líneas de byte transporta información valida, anexo A.1. PAR: Señal Tri-Estado. Proporciona paridad para las líneas AD y C/BE. La generación de la paridad es requerida por los agentes PCI (maestro y dispositivo) en las fases de dirección, escritura y lectura de datos..

(25) Figura 1.6 Disposición de señales de E/S en el bus local PCI Líneas de Control de Interfaz FRAME#: Señal Tri-Estado Sostenida. Es manejada por el maestro actual para indicar el principio y la duración de una transferencia. Se activan al comienzo y se desactivan cuando el maestro está preparado para finalizar la fase de datos. IRDY#: Señal Tri-Estado Sostenida. La proporciona el maestro actual del bus (iniciador de la transacción), Iniciador Preparado (Initiator Ready). Durante una lectura, indica que el maestro está preparado para aceptar datos; durante una escritura indica que el dato válido está en AD. TRDY#: Señal Tri-Estado Sostenida. La proporciona el dispositivo seleccionado o agente objetivo. Dispositivo Preparado (Target Ready) indica durante una fase de lectura que el dato válido está en AD; durante una fase de escritura que el destino está preparado para aceptar datos. STOP#: Señal Tri-Estado Sostenida. Indica que el dispositivo seleccionado desea que el maestro detenga la transacción actual. LOCK#: Señal Tri-Estado Sostenida. Indica una operación atómica que puede requerir múltiples transacciones para ser cumplida. IDSEL: Señal de Entrada. Selector de Inicio de Dispositivo (Initialization Device Select), usada como una señal de selección de circuito (chip select) durante las lecturas y escrituras de configuración..

(26) DEVSEL#: Señal de Entrada. Selector de Dispositivo (Device Select), activada por el dispositivo seleccionado cuando ha reconocido su dirección, indica al maestro actual cuando se ha seleccionado un dispositivo. Líneas de Arbitraje (Bus Masters solamente) REQ#: Señal Tri-Estado. Indica al árbitro que el dispositivo correspondiente solicita utilizar el bus. Línea punto a punto específica para cada dispositivo. Cada maestro tiene su propia línea REQ#, la que debe ser llevada a Tri-Estado mientras RST# es activada. GNT#: Señal Tri-Estado. Indica al dispositivo que el árbitro le ha cedido el acceso al bus. Es una señal punto a punto. Cada master tiene su propia línea GNT#, la que debe ser llevada a Tri-Estado mientras RST# es activada. Cualquier dispositivo de un bus PCI que es capaz de actuar como maestro de bus puede iniciar una transacción con cualquier otro dispositivo. Para asegurarse de que sólo una transacción se inicia a la vez, cada maestro debe esperar primero a un bus de señal de concesión, GNT #, a partir de un árbitro situado en la placa base. Cada dispositivo tiene una línea de petición REQ # independiente que solicita el empleo del bus. El árbitro puede eliminar GNT # en cualquier momento y el dispositivo que pierde este permiso puede completar su transacción actual (Cortés Romero et al., 2001). Mientras RST# está activa, el árbitro debe ignorar todas las señales REQ# dado que están en Tri-Estado (alta impedancia) y no implican requerimientos válidos. Líneas de Reporte de Errores PERR#: Señal Tri-Estado Sostenida. Error de Paridad (Parity Error), indica que se ha detectado un error de paridad en los datos por parte del dispositivo en el caso de una escritura, o por parte del maestro en el caso de una lectura. SERR#: Señal Drenador Abierto. Error del Sistema (System Error), la puede activar cualquier dispositivo para comunicar errores de paridad en la dirección u otro tipo de errores críticos distintos de la paridad. Líneas de Interrupción Las interrupciones en el bus PCI son activas en nivel bajo, usando drivers (controladores) con salidas Drenador Abierto. Un dispositivo activa a INTX# cuando requiere atención. Una vez que esta línea está activa, se mantiene así hasta que el dispositivo interrumpido atiende al requisito. Cuando se termina de atender, el dispositivo desactiva la línea de interrupción utilizada..

(27) Líneas de Soporte de Cache SBO: Señal Bidireccional. Snoop Backoff, indica un acceso a una línea de cache modificada. SDONE: Señal Bidireccional. Snoop Done, indica el estado del módulo de sondeo del bus en acceso actual a cache. Se activa cuando el sondeo ha terminado (Villar, n.d.). 1.3.2. Secuencia de una transacción del bus PCI El tráfico de información que se produce en el bus PCI es generado por una serie de transacciones, cada una de las cuales compuestas por una fase de direccionamiento seguida por una o más fases de datos. El sentido de las fases de datos pueden ser del iniciador al destino (transacción de escritura) o viceversa (transacción de lectura), pero todas las fases de datos deben suceder en el mismo sentido. Las transacciones de bus PCI son controladas por cinco señales principales, dos impulsadas por el iniciador de una transacción (FRAME # y IRDY #), y tres impulsadas por el objetivo (DEVSEL #, # TRDY, y STOP #). Existen dos señales adicionales de arbitraje (REQ # y GNT #) que se utilizan para obtener el permiso para iniciar una transacción. Todos son activos en nivel bajo, lo que significa que el estado activo o afirmado es una tensión baja, por ello se emplean en la placa base resistencias de Pull-Up para asegurar que se mantendrán en alto (inactivo o denegado) si no son solicitados por ningún dispositivo. A continuación en la figura 1.7, se muestra la temporización de una operación de lectura típica; las operaciones de escritura se producen de forma análoga. Todos los eventos se sincronizan en las transmisiones de bajada del reloj, cosa que sucede a la mitad de cada ciclo de reloj. Los dispositivos del bus interpretan las líneas del bus en los flancos de subida al comienzo del ciclo de bus. Seguidamente se describen los eventos significativos señalados en el diagrama: a) Una vez que el maestro del bus ha obtenido el control, debe iniciar la transacción activando FRAME. Esta línea permanece activa mientras que el maestro está dispuesto a terminar la última fase de datos. El maestro también sitúa la dirección de destino en las 32 líneas del bus de direcciones, y el comando asociado a la orden de lectura en las líneas C/BE. b) Al comienzo del ciclo de reloj 2, el dispositivo del que se lee reconocerá su dirección en las líneas AD. c) El maestro deja libres las líneas AD del bus. En todas las líneas de señal que pueden ser activadas por más de un dispositivo se necesita un ciclo de cambio (indicado por las dos flechas circulares) para que la liberación de las líneas de dirección permita que.

(28) el bus pueda ser utilizado por el dispositivo de lectura. Sin esto, puede haber un período en que ambos dispositivos estaban conduciendo la señal, que pudiera interferir con la operación del bus. El maestro cambia la información de las líneas C/BE para indicar cuales de las líneas AD se utilizan para transferir el dato direccionado (de 1 a 4 bytes). El maestro también activa IRDY para indicar que está preparado para recibir el primer dato.. Figura 1.7 Operación de lectura en el bus PCI d) El dispositivo de lectura seleccionado, responde como objetivo y activa DEVSEL para indicar que ha reconocido las direcciones y va a responder. Sitúa el dato solicitado en las líneas AD y activa TRDY para indicar que hay un dato válido en el bus. e) El maestro lee el dato al comienzo del ciclo de reloj 4 y cambia las líneas de habilitación de byte según se necesite para la próxima lectura. f) En este ejemplo, el dispositivo de lectura necesita algún tiempo para preparar el segundo bloque de datos para la transmisión. Por consiguiente, desactiva TRDY para señalar al maestro que no proporcionará un nuevo dato en el próximo ciclo. En consecuencia, el maestro no lee las líneas de datos al comienzo del quinto ciclo de reloj y no cambia la señal de habilitación de byte durante ese ciclo. El bloque de datos es leído al comienzo del ciclo de reloj 6..

(29) g) Durante el ciclo 6, el dispositivo de lectura sitúa el tercer dato en el bus. No obstante, en este ejemplo, el maestro todavía no está preparado para leer el dato (por ejemplo, puede tener lleno el registro de almacenamiento temporal). Para indicarlo desactiva IRDY. Esto hará que el dispositivo de lectura mantenga el tercer dato en el bus durante un ciclo de reloj extra. h) El maestro sabe que el tercer dato es el último, y por eso desactiva FRAME para indicar al dispositivo de lectura que este es el último dato a transferir. Además activa IRDY para indicar que está listo para completar la transferencia. i) El maestro desactiva IRDY, haciendo que el bus vuelva a estar libre, y el dispositivo de lectura desactiva TRDY y DEVSEL (Villar, n.d.). 1.4. Conexión de una tarjeta PCI con un dispositivo FPGA Durante los últimos años en el área de computación reconfigurable se ha visto un gran desarrollo de lo que se llama “computadora reconfigurable”. El escenario más común es una computadora “host” que tiene conectado a su bus PCI una tarjeta aceleradora basada en un FPGA. Las computadoras reconfigurables permiten desarrollar aplicaciones que requieren una ruta de datos o “datapath” cambiante o una unidad aceleradora de hardware (HW) implementada dentro del FPGA con requerimientos específicos (Berrocal, 2007). El bus PCI es el estándar actual para la conexión de tarjetas en una PC. Permite conectar placas que le agregan funcionalidades, por ejemplo placas de sonido, capturadoras de video, placas de red, co-procesadores matemáticos, entre otras. Estas tarjetas suelen llamarse placas PCI. Haciendo énfasis en la adaptabilidad de la placa a la aplicación a desarrollar, la electrónica que la conforme debe ser fácilmente modificable. Hoy día, este objetivo se logra utilizando circuitos integrados de lógica reconfigurable, como son los FPGA. Un FPGA puede verse como una caja llena de biestables (flip-flops), compuertas lógicas y memorias RAM, que pueden ser interconectados de una cierta manera, a gusto del usuario, al configurarlo. El diseño de prototipos de placas PCI, ya sea para su posterior uso comercial o con fines investigativos, se ve acelerado si se comienza a desarrollar a partir de una placa de propósito general, ya existente, que pueda ser rápidamente adaptada según las necesidades del diseño. Partiendo de una placa PCI cuyo núcleo sea un FPGA, el diseño de un prototipo consistirá básicamente en realizar, en algún lenguaje de descripción de circuitos (hardware), un proyecto que configure el FPGA para que se comporte según los requerimientos establecidos. Como un FPGA puede reconfigurarse, en caso de detectar un error en el funcionamiento, basta corregir el error y volver a configurar el FPGA..

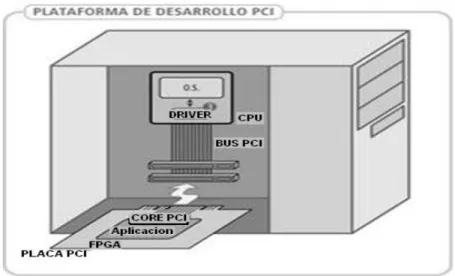

(30) El diseño a programar en el FPGA debe implementar la funcionalidad que se desea agregar a la PC y debe comunicarse utilizando el bus PCI. Dada la complejidad del bus PCI, este diseño podría separarse en dos bloques, uno que resuelva la comunicación con el bus y otro que implemente la funcionalidad. El bloque que resuelve la comunicación es llamado Core PCI y se encarga de encapsular los detalles del estándar (manejo de errores, decodificación de direcciones, señalizaciones, etc.). El resultado final del proyecto es una plataforma de desarrollo para diseños de hardware que utilizan el bus PCI (Fernández et al., 2003).. Figura 1.8 Plataforma de desarrollo PCI Componen la plataforma: . Placa de propósito general con un conector para bus PCI y lógica reconfigurable. Diseño modular (Core PCI) que encapsula los detalles de funcionamiento del bus PCI, para ser utilizado por la aplicación que se configura en el FPGA. Software controlador (driver) que permite que desde programas ejecutándose en un PC se pueda acceder a la placa.. 1.4.1. Dispositivo programable FPGA Una FPGA (del inglés Field Programmable Gate Array) es un dispositivo semiconductor que contiene bloques de lógica cuya interconexión y funcionalidad puede ser configurada 'in situ' mediante un lenguaje de descripción especializado. La lógica programable puede reproducir desde funciones tan sencillas como las llevadas a cabo por una puerta lógica o un sistema combinacional hasta complejos sistemas en un chip..

(31) Una FPGA (del inglés Field Programmable Gate Array), es un dispositivo semiconductor que contiene bloques de lógica cuya interconexión y funcionalidad se puede programar. Se entiende por dispositivo programable aquel circuito de propósito general que posee una estructura interna que puede ser modificada por el usuario final (o a petición suya, por el fabricante) para implementar una amplia gama de aplicaciones. La lógica programable puede reproducir desde funciones tan sencillas como las llevadas a cabo por una puerta lógica o un sistema combinacional hasta complejos sistemas en un chip (circuito integrado). Las FPGA, son el dispositivo programable por el usuario de más general espectro. También se denominan LCA (Logic Cell Array). Consisten en una matriz bidimensional de bloques configurables. En el nivel más alto, los FPGAs son chips de silicio reprogramables. Al utilizar bloques de lógica pre-construidos y recursos para ruteo programables, se pueden configurar estos chips para implementar funcionalidades personalizadas en hardware, solo desarrollando tareas de cómputo digital en software y compilándolas en un archivo de configuración o bitstream que contenga información de cómo deben conectarse los componentes. Además, los FPGAs son completamente reconfigurables y al instante toman una nueva “personalidad” cuando se compila una diferente configuración de circuitos (M. L. López Vallejo y J. L. Ayala Rodrigo, 2004). Las FPGAs fueron inventadas en el año 1984 por los co-fundadores de Xilinx (Empresa de investigación y desarrollo de FPGAs), Ross Freeman y Bernard Vonderschmitt, y surgen como la evolución "natural" de los CPLDs (dispositivos lógicos programables complejos). Las diferencias fundamentales están relacionadas con la densidad de compuertas lógicas, en las FPGAs existen desde cientos de miles a millones mientras que en los CPLDs decenas de miles, haciendo a estos últimos más rígidos en lo que a alternativas programables se refiere. La arquitectura de las FPGAs, por otro lado, se basa en un gran número de pequeños bloques utilizados para reproducir sencillas operaciones lógicas, que cuentan a su vez con biestables síncronos. La enorme libertad disponible en la interconexión de dichos bloques confiere a las FPGAs su gran flexibilidad. Otra diferencia importante entre FPGAs y CPLDs es que en la mayoría de las FPGAs se pueden encontrar funciones de altos niveles (como sumadores y multiplicadores) desarrolladas en la propia matriz de interconexiones, así como bloques de memoria.(Bozich, 2004) Las FPGAs se utilizan en aplicaciones similares a los ASICs (Integrated Circuit for Applications Specifics) sin embargo son más lentas, tienen un mayor consumo de potencia y no pueden abarcar sistemas tan complejos como ellos. A pesar de esto, las FPGAs tienen la ventaja de ser reprogramables (lo que añade una enorme flexibilidad al flujo de diseño), sus costes de desarrollo y adquisición son mucho menores para pequeñas cantidades de dispositivos y el tiempo de desarrollo es también menor. La adopción de chips FPGA en la industria ha sido impulsada por el hecho de que los FPGAs combinan lo mejor de los ASICs y de los sistemas basados en procesadores. El silicio reprogramable tiene la misma capacidad de.

(32) ajustarse que un software que se ejecuta en un sistema basado en procesadores, pero no está limitado por el número de núcleos disponibles. A diferencia de los procesadores, los FPGAs llevan a cabo diferentes operaciones de manera paralela, por lo que éstas no necesitan competir por los mismos recursos (Altera Corporation, 2013). Principales beneficios de la tecnología FPGA . . . Rendimiento: Aprovechando del paralelismo del hardware, los FPGAs exceden la potencia de cómputo de los procesadores digitales de señales (DSPs) rompiendo el paradigma de ejecución secuencial y logrando más en cada ciclo de reloj. El controlar entradas y salidas (E/S) a nivel de hardware ofrece tiempos de respuesta más veloces y funcionalidad especializada que coincide con los requerimientos de una aplicación. Fiabilidad: Mientras que las herramientas de software ofrecen un entorno de programación, los circuitos de un FPGA son una implementación segura de la ejecución de un programa. Los sistemas basados en procesadores frecuentemente implican varios niveles de abstracción para auxiliar a programar las tareas y compartir los recursos entre procesos múltiples. El software a nivel driver se encarga de administrar los recursos de hardware y el sistema operativo administra la memoria y el ancho de banda del procesador. El núcleo de un procesador sólo puede ejecutar una instrucción a la vez, y los sistemas basados en procesadores están siempre en riesgo de que sus tareas se obstruyan entre sí. Los FPGAs, que no necesitan sistemas operativos, minimizan los retos de fiabilidad con ejecución paralela y hardware preciso dedicado a cada tarea. Mantenimiento a largo plazo: Como se mencionó anteriormente, los chips FPGA son actualizables en campo y no requieren el tiempo y el precio que implica rediseñar un ASIC. Los protocolos de comunicación digital por ejemplo, tienen especificaciones que podrían cambiar con el tiempo, y las interfaces basadas en ASICs podrían causar retos de mantenimiento y habilidad de actualización. Los chips FPGA, al ser reconfigurables, son capaces de mantenerse al tanto con modificaciones a futuro que pudieran ser necesarias. Mientras el producto o sistema se va desarrollando, usted puede implementarle mejoras funcionales sin la necesidad de invertir tiempo rediseñando el hardware o modificando el diseño de la tarjeta (Nationals Instruments, n.d.).. 1.5. Conclusiones del capítulo Los principios de la Ingeniería Inversa son aprovechados a nivel internacional por numerosas instituciones, basados en las posibilidades que brindan para asimilar nuevas tecnologías, que sin el poder conferido por legítimas creaciones, derechos reservados y capital, cuentan con la capacidad y el ingenio para reproducir técnica y aplicaciones..

(33) La presente investigación está relacionada con el intercambio de información por medio de señales con funciones específicas que circulan a través de líneas especializadas, contorno al que se le conoce como Bus de datos. Es esencial para el desarrollo de esta labor la comprensión de las características básicas del Bus local PCI y de su modo de operación, que se encuentra gobernado por un dispositivo programable..

(34) CAPÍTULO 2. LA TARJETA 811 DENTRO DEL COMPLEJO DE DEFENSA. CARACTERIZACIÓN. En nuestro país la labor de renovación tecnológica en las Fuerzas Armadas Revolucionarias (FAR) está sostenida por una certera política científica, que en lugar de reemplazar el material de guerra existente, destaca el trabajo de ingenieros e innovadores quienes logran su modernización, actividad que representa en la actualidad una solución económica más viable, mostrando significativos resultados. La Defensa Antiaérea de las FAR (DAAFAR), primordial entidad, encargada de preservar la integridad del espacio aéreo cubano, de igual forma está comprometida con la revolución técnica que acontece. Posteriormente se analizará la disposición estructural de la tecnología adquirida con atención en ubicar y caracterizar dentro del conjunto la tarjeta programable 811, contenido de la investigación. 2.1. La electrónica implementada en el sistema de defensa antiaéreo Dentro del proyecto para la modernización y el desarrollo del armamento, que lleva a cabo la DAAFAR, se encuentra la estación de vigilancia del espacio aéreo S75MK-102 “VOLGA” a la cual se le digitalizó la cabina de mando. En el sistema de defensa antiaéreo “VOLGA” hay en total dieciocho tarjetas las cuales se encuentran funcionando, de ellas cinco (denominadas T138, T139, T232, T335 y T811) están implementadas con electrónica programada y solo se conoce su finalidad dentro del complejo, no así su modo de funcionamiento (Pierrat, 2010). Las 13 tarjetas restantes están conformadas con electrónica analógica y digital, conociéndose su esquema electrónico y su funcionamiento completamente. En el esquema que se muestra a continuación, figura 2.1, se ofrecen detalles sobre el enlace de comunicación entre las tarjetas programables y los componentes principales de este dominio. . Caja eléctrica BK1 para el intercambio de señales con la cabina de antenas. Caja eléctrica BK3, para el intercambio de señales con las rampas de lanzamiento (RL). Puesto de trabajo 120, para el operador de distancia. Puesto de trabajo 220, para el operador de ángulo de elevación (E). Puesto de trabajo 320, para el operador de azimut (B). Monitor 110, para el trabajo del operador de distancia. Monitor 210, para el trabajo del operador de ángulo de elevación (E). Monitor 310, para el trabajo del operador de azimut (B). Computadora de control del tiro, para el trabajo del Jefe al mando..

(35) Figura 2.1 Enlace funcional del sitema digitalizado Tarjeta 132 para distribuir las señales que se aplican a los receptores. Tarjeta 134 en función de receptor, por el plano de elevación (E), para amplificar las señales de frecuencia intermedia que llegan desde la cabina de antenas y convertirlas en señales de video, por el canal del blanco (aviones) y los canales de los artículos (cohetes). Tarjeta 135 en función de receptor, por el plano de azimut (B), para amplificar las señales de frecuencia intermedia que llegan desde la cabina de antenas y convertirlas en señales de video, por el canal del blanco y los canales de los artículos. Tarjeta 331 para recibir los impulsos de los emisores de las antenas y llevarlos al voltaje adecuado al trabajo de los componentes digitales. Tarjeta 332 para amplificar los mandos que se envían a la cabina de antenas, desde niveles TTL a niveles de 26v. Tarjeta 3310 para amplificar los impulsos que se envían a la cabina de antenas, desde niveles TTL a niveles de más de 40V. Tarjetas 333 y 334, para la conversión de los mandos que se envían hacia las rampas de lanzamiento desde niveles TTL a niveles de +26v y también para bajar los voltajes de las señalizaciones que llegan de las rampas de lanzamiento, desde niveles de +26v a.

(36) . . . . . . . . niveles TTL, adecuados al trabajo de los componentes digitales. La T333 dedicada a las RL 1, 2 y 3; la T334 para las RL 4, 5 y 6. Tarjeta 231 para obtener la referencia de la posición de las antenas y las RL, convirtiendo las fases de los selsines transmisores y de indicación en código binario, por los planos B y E. Tarjeta 233 para amplificar las señales de mando de giro del motor que introduce la predicción en el ángulo de tiro de las RL. Tarjetas 234 y 235, para amplificar los mandos de giro del motor que introduce el ángulo deseado de orientación de las antenas. La T234 dedicada al plano E y la T235 para el plano de azimut. Los bloques 430 y 440 que contienen los motores, selsines y mecanismos, a través de los cuales se introducen las posiciones de las antenas y RL. El bloque 430 dedicado al plano E y el 440 para el plano de azimut. Tarjeta 335 (sincronizador) está implementada con electrónica programada, en ella se elaboran los impulsos de sincronismo de la transmisión y la recepción de señales, así como la atención a las conmutaciones e indicaciones de los paneles de los bloques 320 y 420. Tarjeta 232 (SDA) está implementada con electrónica programada, sirve de enlace con la tarjeta 138 para indicar la dirección de las antenas, las RL y para la atención a las variaciones en el panel del bloque 220. Tarjeta 139 (Imitador) está implementada con electrónica programada, sirve para conformar las señales de video que reproducen escenarios de combate (simulando condiciones reales) y para la atención a las variaciones en el panel del bloque 120. Tarjeta 811 (PCI) que está implementada con electrónica programada, sirve para el intercambio de información entre la computadora de control del tiro y el resto del sistema. Tarjeta 138 (Cálculo) que está implementada con electrónica programada, en ella se realizan todos los algoritmos y cálculos fundamentales para el funcionamiento de todos los módulos de complejo.. 2.2. Tarjeta 811 para la interconexión de componentes periféricos La transferencia de datos a través del dispositivo PCI incrementa las posibilidades de conexión con el resto del sistema y acelera el procesamiento de la información que se intercambia con el software de supervisión y entrenamiento. El mecanismo de diseño digital que emplea la T811 se rige por el modo en que se realiza el intercambio de los indicadores posicionales y de estado que conforman la aplicación. Los cambios de posiciones del blanco, la distancia a la que se encuentra y sus coordenadas angulares (β: azimut-barrido horizontal y ξ: elevación-barrido vertical), son elementos que llegan a la computadora de control como.

(37) resultado de las operaciones realizadas en la tarjeta de cálculo 138 reflejando la disposición técnica de la Estación de Vigilancia; que a su vez deben ser conocidos por la tarjeta de salida de video 139 para que esta pueda representarlos en el monitor de cada uno de los puestos de trabajo encargados de tomar nuevas decisiones de disparo, dar seguimiento y corregir el tiro.. Figura 2.5 Tarjeta 811 PCI y su conector La imagen de la T811 se muestra en la figura 2.5, se puede observar que está diseñada para insertarla en un slot universal (3.3 y 5V) de la tarjeta madre de la computadora, exponiendo además la relación de señales de entrada y salida en su conector (DB-37). Para el proceso de análisis no se dispone de esquema electrónico ni de esquema funcional. Las señales que fluyen multiplexadas a través de esta interfaz serie son SB1, SB2, SB3 y SB4. La estructura de los datos que contienen cada señal SB no se conoce aún, ésta puede determinarse a partir de la interpretación del programa fuente, lenguaje de programación VHDL, que se encuentra en el componente programable FPGA EP2C70F896C8 de la tarjeta PCI. 2.2.1. Modo de comunicación empleado en las tarjetas programadas El óptimo desempeño de un sistema de comunicación depende del protocolo de transmisión de datos que sea empleado y de la calidad de la señal que se reciba. Pero esta calidad se degrada a medida que aumenta la distancia entre emisor y receptor. En consecuencia, la separación física entre los dispositivos programados (T138, T139, T232, T335 y T811) que.

(38) intercambian información en el sistema defensivo es uno de los factores que determina el formato de las señales SB (Bus Serie) para garantizar la efectividad de la transmisión. Los parámetros técnicos relacionados con el sistema de giro de las antenas, con la disposición de las rampas de lanzamiento, con la trayectoria del recorrido de los aviones, entre otros, es el tipo de información que portan estas señales SB1, SB2, SB3, SB4, SB18 y SB19. La representación detallada del enlace y los puertos que interconectan cada una de estas señales con sus respectivos módulos se muestran en la figura 2.2 (Pierrat, 2013b).. Figura 2.2 Comunicación bus serie (SB) entre las tarjetas Transmisión serie En la transmisión serie un bit sigue a otro, por lo que solamente se necesita un canal de comunicación, en lugar de n, para transmitir datos entre dos dispositivos, figura 2.3. La ventaja sobre la transmisión paralela es que, al tener un único canal de comunicación, reduce el coste de transmisión en un factor de n y por tanto se emplea cuando es preciso intercambiar información a distancia..

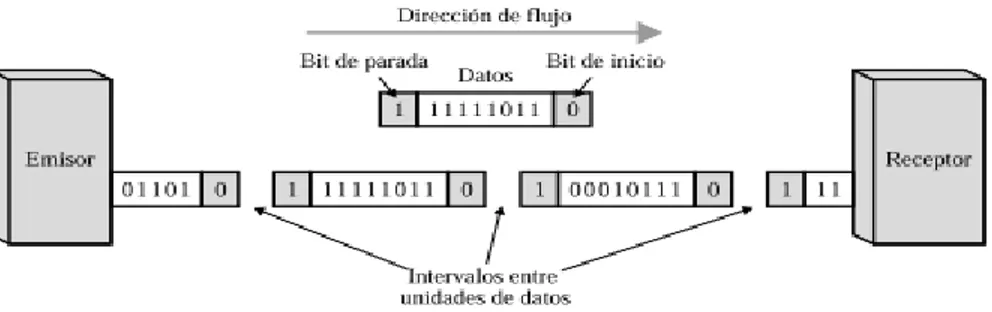

(39) La comunicación dentro de los dispositivos es paralela por posibilitar mayores velocidades de transferencias, necesarias para el procesamiento de los datos, entonces se deben usar dispositivos de conversión en la interfaz entre el emisor y la línea (paralelo a serie) y entre la línea y el receptor (serie a paralelo). La transmisión serie puede llevarse a cabo de dos maneras: asíncrona y síncrona. Trataremos la transmisión asíncrona por converger con las características de nuestro sistema de comunicaciones.. Figura 2.3 Transmisión Serie Transmisión Serie Asíncrona La transmisión asíncrona se denomina así debido a que la temporización de la señal no es determinante para establecer la comunicación entre los extremos. En lugar de ella, la información se recibe y se traduce usando patrones acordados. Siempre que se sigan estos patrones, el dispositivo de recepción puede recuperar la información sin tener en cuenta el ritmo al que llega. Los patrones se basan en agrupar el flujo de bits en bytes. Cada grupo, habitualmente de ocho bits, se envía a lo largo de un enlace como una unidad. El sistema que lo envía gestiona cada grupo independientemente, entregándolo al enlace en cuanto está listo, sin tener en cuenta ninguna temporización. Sin la existencia de un pulso de sincronización, el receptor no puede usar el tiempo para predecir cuándo va a llegar el grupo siguiente. Por ello, para avisar al receptor de la llegada de un nuevo grupo se añade un bit extra al principio de cada byte. Este bit, habitualmente un cero, se denomina bit de inicio. Para permitir al receptor conocer que el byte ha terminado, se añaden uno o varios bits adicionales al final de cada byte. Estos bits, habitualmente unos, se denominan bits de parada. Usando este método, el tamaño de cada byte se incrementa hasta al menos diez bits, de los cuales ocho son información y dos, o más, son señales para el receptor. Además, la transmisión de cada byte puede venir seguida por un intervalo de duración variable. Este intervalo se puede representar mediante un canal vacío o mediante una cadena de bits de parada adicionales. Los bits de inicio, de parada y el intervalo alertan al receptor del comienzo y el fin de cada byte y le permiten sincronizarse con el flujo de datos. Este mecanismo se denomina asíncrono porque el emisor y el receptor no tienen que estar sincronizados a nivel de byte..

Figure

+7

Outline

Tarjeta 811 para la interconexión de componentes periféricos

Declaraciones de los componentes Descripción estructural de hardware

Secuencia que rige el acceso al bus local PCI durante etapas de configuración, de

Conclusiones del Capítulo

Descripción básica del Quartus II

Código fuente de la tarjeta 811 PCI

Documento similar