Interfaz para adquisición dedatos con FPGA de Altera

Texto completo

(2) Universidad Central “Marta Abreu” de Las Villas Facultad de Ingeniería Eléctrica Departamento de Telecomunicaciones y Electrónica. TRABAJO DE DIPLOMA “Interfaz para adquisición de datos con FPGA de Altera” Autor: José Juan Hernández Cabrera Tutor: Dr. Juan Pablo Barrios Rodríguez Prof. Dpto. de Telecomunicaciones y electrónica e-mail: barrios@uclv.edu.cu Consultante: MSc. Ivan Iglesias Navarro Prof. Dpto. de Automática y Sistemas Computacionales e-mail: iglesias @uclv.edu.cu. Santa Clara 2007 "Año 49 de la Revolución".

(3) Hago constar que el presente trabajo de diploma fue realizado en la Universidad Central “Marta Abreu” de Las Villas como parte de la culminación de estudios de la especialidad de Ingeniería en Telecomunicaciones y Electrónica, autorizando a que el mismo sea utilizado por la Institución, para los fines que estime conveniente, tanto de forma parcial como total y que además no podrá ser presentado en eventos, ni publicados sin autorización de la Universidad.. Firma del Autor. Los abajo firmantes certificamos que el presente trabajo ha sido realizado según acuerdo de la dirección de nuestro centro y el mismo cumple con los requisitos que debe tener un trabajo de esta envergadura referido a la temática señalada.. Firma del Autor. Firma del Jefe de Departamento donde se defiende el trabajo. Firma del Responsable de Información Científico-Técnica.

(4) i. PENSAMIENTO. “En las actuales sociedades, lo imaginativo cede su cetro a lo inteligente; lo realizable se hace dueño de lo que dominaba antes lo soñado; lo práctico se impone en nuestros tiempos con una soberbia fatal y poderosa” José Martí (1875).

(5) ii. DEDICATORIA. A: Mi familia, en especial a mis padres, por ser mi ejemplo y mi guía, quienes me han apoyado tanto y esperado tan apasionadamente este día..

(6) iii. AGRADECIMIENTOS. A: Mi familia, en especial a mi tío Roberto. A: Mi tutor Dr. Juan Pablo Barrios Rodríguez. A: Mi tutor Consultante: MSc. Ivan Iglesias Navarro. A: Yaima, mi novia. A: Todos mis compañeros de curso que me han ayudado cuando los he necesitado a lo largo de toda la carrera. A: Todo el que de una forma u otra apoyó en la realización de este Trabajo de Diploma. A: Todo el que de una forma u otra contribuyó en mi formación como profesional.. A todos, Muchas Gracias.

(7) iv. TAREA TÉCNICA. Como Tareas Técnicas necesarias para cumplir con el objetivo y las interrogantes de la presente investigación se plantean:. 1. La realización de una revisión de la literatura científica y técnica que permita identificar las regularidades del proceso de diseño electrónico digital, con vistas a su desarrollo dentro del proceso de enseñanza-aprendizaje. 2. La caracterización y el análisis de FPGAs de Altera, que nos permita su utilización para fines docentes. 3. El estudio del software Quartus II de Altera para su explotación en la implementación de una interfaz para la adquisición de datos, acoplada al ordenador. 4. La implementación y comprobación de esta aplicación. 5. El análisis y evaluación de los resultados obtenidos tal que nos permita proponer la utilización de esta tecnología como recurso tecnológico-docente. 6. La redacción del Informe Final.. Firma del Autor. Firma del Tutor.

(8) v. RESUMEN. Las nuevas transformaciones que están sucediendo en el panorama del desarrollo de las telecomunicaciones y la electrónica en el país, han llevado al Ministerio de la Informática y las Comunicaciones a redefinir la estrategia del desarrollo de la electrónica. Dentro de dichas transformaciones se encuentran, el desarrollo de hardware digital y la aplicación del procesamiento digital de señales (DSP) en diversas áreas. Esta investigación tiene como objetivo desarrollar el hardware y la metodología para el diseño de un sistema de adquisición de datos, acoplado al ordenador utilizando dispositivos lógicos programables del tipo FPGA (Field Programmable Gate Arrays). Para ello fue necesario abarcar aspectos relacionados con las diferentes arquitecturas de FPGAs, el lenguaje de descripción de hardware VHDL (IEEE-1076/93), las Máquinas de Estado Algorítmico (ASM) y la metodología de diseño electrónico digital, permitiendo así la implementación de un sistema de adquisición de datos, en un entorno de trabajo con un computador y un kit de entrenamiento con el APEX EP20K100EQC240-2X, configurable desde el propio ordenador. Dicha aplicación constituye un significativo aporte al conjunto de prácticas de media a alta complejidad que se desarrollan como apoyo docente a las asignaturas de Electrónica Digital I y II, en nuestra facultad. Además, se muestran los resultados tanto en simulaciones de software como en demostraciones con hardware que posibilitan una mejor preparación docente e investigativa de los estudiantes de la carrera de Ingeniería en Telecomunicaciones y Electrónica..

(9) vi. ÍNDICE. PENSAMIENTO.......................................................................................................................... i DEDICATORIA ..........................................................................................................................ii AGRADECIMIENTOS .............................................................................................................. iii TAREA TÉCNICA ..................................................................................................................... iv RESUMEN ................................................................................................................................ v INTRODUCCIÓN ....................................................................................................................... 1 CAPÍTULO I. GENERALIDADES SOBRE EL DISEÑO DIGITAL UTILIZANDO FPGAs ..................................................................................................................................... 5 I.1. El diseño digital visto como competencia profesional. ......................................................... 5 I.1.1. Evolución Histórica del diseño electrónico digital. ......................................................... 5 I.1.2. Invariantes funcionales de la habilidad diseñar en electrónica digital ............................. 9 I.2. Definiciones básicas acerca de los lenguajes de descripción de hardware. ........................... 9 I.2.1. El lenguaje VHDL. Sus ventajas para el diseño de sistemas digitales. .......................... 11 I.3. Sistema convertidor de datos. ......................................................................................... 13 I.4. Ventajas que presenta la utilización de FPGAs. ................................................................ 13 I.5. Conclusiones parciales del capítulo. ................................................................................ 15 CAPÍTULO II. PARTICULARIDADES DEL HARDWARE UTILIZADO E INTRODUCCIÓN AL QUARTUS II............................................................................................................................ 16 II.1. Breve descripción del Conversor A/D (ADC0804LCN). ..................................................... 16.

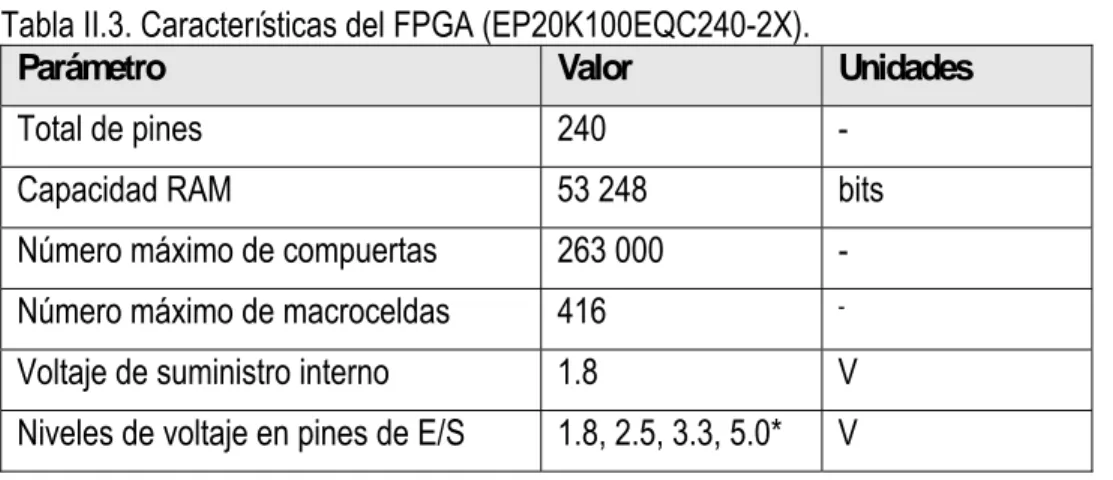

(10) vii II.2. Características generales de las FPGAs y los CPLDs de la firma Altera. La Familia APEX 20K......................... .............................................................................................................. 17 II.2.1. Descripción General. ............................................................................................... 17 II.2.2. Descripción funcional. ............................................................................................. 18 II.2.3. Estructura de MegaLAB........................................................................................... 19 II.2.4. Bloque de arreglo lógico. ......................................................................................... 20 II.2.5. Elemento lógico. ..................................................................................................... 22 II.2.6. Modos de operación del LE. .................................................................................... 24 II.2.6.1. Modo normal. ............................................................................................................24 II.2.6.2. Modo aritmético. .......................................................................................................26 II.2.6.3. Modo contador. .........................................................................................................26 II.2.7. Lógica de Término-Producto ............................................................................................27 I.3.2. Características del Kit que contiene al FPGA. ................................................................32 II.4. Conclusiones parciales del capítulo................................................................................. 39 CAPÍTULO III APLICACIÓN DE ADQUISICIÓN DE DATOS CONTROLADO POR FPGA, ACOPLADA AL ORDENADOR ................................................................................................. 40 III.1. Introducción. ................................................................................................................ 40 III.2. Especificación del problema. ......................................................................................... 40 III.3. Utilización del modelo. .................................................................................................. 42 III.3.1. Explicación del diagrama ............................................................................................ 42 III.4. Implementación. ........................................................................................................... 51 III.4.1. Simulación del adquisidor. .......................................................................................... 52 III. 5. Implementación en hardware del algoritmo de adquisición de datos. ................................ 55 III. 6. Resultados de la implementación. ................................................................................. 55 III.7. Conclusiones parciales del capítulo. ............................................................................... 56.

(11) viii CONCLUSIONES .................................................................................................................... 57 RECOMENDACIONES............................................................................................................. 58 REFERENCIAS BIBLIOGRÁFICAS ........................................................................................... 59 ANEXOS ................................................................................................................................. 61 Anexo 1: Diagrama de estados realizado para la implementación del diseño. .............................. 61 Anexo 2: Descripción en lenguaje VHDL que se obtuvo a partir del ASM. ..................................... 62 Anexo 3: Puesto de trabajo para la realización de pruebas al hardware. ....................................... 66 Anexo 4: Sistema de adquisición de datos. ................................................................................ 66 Anexo 5: Base de datos donde se almacenan las muestras adquiridas. ........................................ 67.

(12) INTRODUCCIÓN. 1. INTRODUCCIÓN. El procesamiento electrónico-digital de señales es un área de la ciencia y la ingeniería que se ha desarrollado rápidamente durante los últimos 30 años. Este rápido desarrollo es el resultado de los avances tecnológicos tanto en los ordenadores digitales como en la fabricación de circuitos digitales de muy alta escala de integración. Los ordenadores digitales y el hardware asociado hace tres décadas eran relativamente grandes y caros y como consecuencia, su uso se limitaba a aplicaciones de propósito general en tiempo no real, tanto científicas como comerciales. El rápido desarrollo de la tecnología de circuitos integrados, empezando con la integración a mediana escala (MSI, Medium-Scale Integration) y continuando la integración a gran escala (LSI, Large-Scale Integration), hasta llegar a la integración a muy gran escala (VLSI, Very-Large-Scale Integration) de circuitos electrónicos ha estimulado el desarrollo de ordenadores digitales más potentes, pequeños, rápidos, baratos y de hardware digital de propósito general. Lo anterior ha hecho posible construir sistemas digitales altamente sofisticados, capaces de realizar funciones y tareas de procesamiento digital de señales que normalmente eran demasiado difíciles y/o caras con circuitería o sistemas de procesamiento de señales analógicas. De aquí que muchas de las tareas del procesamiento de señales que convencionalmente se realizaban analógicamente se realicen hoy mediante hardware digital, más barato y a menudo más fiable. Las nuevas transformaciones que están sucediendo en el panorama del desarrollo de las telecomunicaciones y la electrónica en el país han llevado al Ministerio de la Informática y las Comunicaciones (MIC) a redefinir la estrategia del desarrollo de la electrónica. Dentro de dichas transformaciones se encuentra la aplicación del procesamiento (con hardware) digital de señales en campos tan diversos como las comunicaciones, los equipos electrónicos y las aplicaciones computacionales en general..

(13) INTRODUCCIÓN. 2. En estos aspectos, el país ha dirigido grandes esfuerzos y recursos que incluyen la compra e instalación de equipamiento con tecnologías de último modelo y la realización de eventos científicos de orden nacional e internacional con el objetivo de capacitar especialistas que dominen estas tecnologías. En este sentido, resulta estratégico preparar una docencia de mayor calidad en la carrera de Ingeniería en Telecomunicaciones y Electrónica, la cual tiene la responsabilidad de formar profesionales con alta preparación en las técnicas de diseño electrónico digital moderno. Contar con un conjunto de aplicaciones típicas sobre dispositivos lógicos programables del tipo FPGA (Field Programmable Gate Arrays en inglés) en un kit de entrenamiento para estos fines, permitirá una mejor preparación docente e investigativa de los estudiantes de la especialidad antes mencionada y/o personal orientado a la misma. La estrategia metodológica del colectivo de las asignaturas de Electrónica Digital I y II tiene dentro de sus objetivos, contar de un grupo de diseños, utilizando el Quartus II de Altera y un kit de entrenamiento con el APEX EP20K100EQC240-2X, factible de configurar desde el propio ordenador, así como las interfaces necesarias para la comprobación, sobre el kit, de los diseños programados. La necesidad social de formación de especialistas de la carrera antes citada, unido a las experiencias en la investigación científica relacionada con el diseño digital y el procesamiento digital de señales, las cuales se concentran fundamentalmente en el CEETI (Centro de Estudios de Electrónica y Tecnología de la Información) y el departamento de Telecomunicaciones y Electrónica [Barrios, 2002, 2004, 2006], [Taboada, Mendoza, Lorenzo y Lovely 2003], [Taboada, Mendoza y Lorenzo 2004, pp. 1199-1202], en conjunto con la experiencia docente-metodológica en las asignaturas de Electrónica Digital, Fundamentos de las Comunicaciones, Procesamiento Digital de Señales, entre otras, han propiciado una cultura científica y tecnológica sobre esta temática reconocida en el contexto nacional. En el departamento de Telecomunicaciones y Electrónica, por su parte, existe experiencia en el diseño digital, explotando las facilidades de las herramientas de ayuda al diseño (EDA en inglés) [Barrios, 2000], [Barrios, 2002], [Barrios, 2003], [Barrios, 2005], [Barrios, 2006] y los dispositivos digitales de alta escala de integración configurables (PLD ó FPGA). Dicha experiencia se ha revertido en una docencia con altos niveles de satisfacción estudiantil en las carreras de Telecomunicaciones y Electrónica y de Automática..

(14) INTRODUCCIÓN. 3. Las recientes demandas de profesionales competentes en el diseño, instalación y mantenimiento de equipos con alta tecnología digital y de gran procesamiento digital de señales, han llevado a la decisión de profundizar en la preparación docente de las asignaturas relacionadas con estas temáticas, con el objetivo de que los estudiantes adquieran los conocimientos y habilidades fundamentales en el diseño de sistemas digitales básicos de su campo de acción profesional. En este sentido, desarrollar una base material y técnica que permita una docencia de calidad en estas asignaturas, es una necesidad impostergable. La necesidad social de formación de especialistas de la carrera antes citada, unido a las experiencias del CEETI y del departamento de Telecomunicaciones y Electrónica en el diseño electrónico digital, utilizando PLDs ó FPGAs conduce a la interrogante fundamental de la presente investigación: Problema Científico ¿Cómo elaborar una metodología de diseño electrónico-digital, utilizando FPGAs, para una aplicación generalizadora de los contenidos y habilidades de la Electrónica Digital, tal que garantice una mejor formación en los estudiantes de Telecomunicaciones y Electrónica? Como se deduce de la interrogante anterior el objeto de estudio de la presente investigación es el relacionado con el desarrollo de diseño de sistemas electrónico digitales típicos, constituyendo el campo de acción; por una parte el diseño e implementación de sistemas digitales complejos sobre FPGAs, y por otra los fundamentos esenciales relacionados con la enseñanza-aprendizaje de la Electrónica Digital. Como Interrogantes Científicas, a solucionar como parte de la investigación se encuentran: 1.. ¿Cuáles son las regularidades del proceso de diseño electrónico digital con vistas a su desarrollo dentro del proceso de enseñanza-aprendizaje?. 2.. ¿Cuál de las familias de FPGAs de Altera, es la más adecuadas para fines docentes?. 3.. ¿Qué facilidades presenta el software Quartus II de Altera para la realización de una interfaz para la adquisición de datos, acoplada al ordenador?. 4.. ¿Cómo implementarla en un hardware de propósito general tal como el kit de entrenamiento?.

(15) INTRODUCCIÓN. 5.. 4. ¿Cómo comprobar y documentar dicha implementación?. Como Objetivo General se deriva: Diseñar y comprobar, mediante una metodología general, una interfaz para la adquisición de datos sobre FPGAs, que permita proponer su utilización como recurso tecnológico-docente en las asignaturas Electrónica Digital I y II de la carrera de Telecomunicaciones y Electrónica. La importancia del presente trabajo se revela en dos vertientes, por la parte tecnológica permite familiarizar a los futuros profesionales con las tecnologías electrónico-digitales modernas, mientras que desde el punto de vista didáctico, enriquece el conjunto de medios de apoyo a la enseñanza de las asignaturas de Electrónica Digital I y II. El mismo tiene una actualidad demostrada, por cuanto vincula aspectos del diseño electrónico digital utilizando metodologías de alto nivel de abstracción en la descripción del hardware y empleando tecnologías de avanzada, tales como las FPGAs. El informe cuenta con introducción, tres capítulos, conclusiones, recomendaciones, bibliografía y anexos. CAPÍTULO I: Se verá que es diseño digital, su evolución. También se abordará el tema de las herramientas utilizadas en el proyecto. CAPÍTULO II: Particularidades del hardware utilizado y el estudio del software Quartus II de Altera. CAPÍTULO III: Realización del diseño de la aplicación de adquisición de datos controlado por la FPGA, acoplada al ordenador..

(16) CAPÍTULO I. GENERALIDADES SOBRE EL DISEÑO DIGITAL UTILIZANDO FPGAs. 5. CAPÍTULO I. GENERALIDADES SOBRE EL DISEÑO DIGITAL UTILIZANDO FPGAs. I.1. El diseño digital visto como competencia profesional. Entre los profesionales de las Telecomunicaciones y la Electrónica, aquellos que se encargan de la actividad de diseño son los que requieren mayor capacidad de adaptación a los cambios producidos por el desarrollo tecnológico que demandan la industria, los servicios y la sociedad en general. Son estos los encargados de solucionar problemas utilizando los conocimientos, los métodos y los componentes y sistemas digitales, exige de ingenieros vinculados a este perfil y del desarrollo de habilidades. I.1.1. Evolución Histórica del diseño electrónico digital. En el DRAE se define diseño como: -. Descripción o bosquejo de alguna cosa, hecho por palabras.. -. Proyecto, plan.. -. Concepción original de un objeto u obra destinados a la producción en serie.. -. Forma de cada uno de estos objetos.. De la misma forma expresa que diseñar es: Hacer un diseño. En el campo de la electrónica digital, algunos autores (Mano, 2000; Wakerly, 2000) señalan como la función actual del diseño digital “la creación de sistemas”, lo que reafirma la complejidad de los circuitos digitales modernos y, por ende, del proceso asociado a su realización. Es importante destacar el término creación en la anterior definición, por cuanto expresa que el diseño electrónico digital requiere, por parte de los profesionales de este perfil, una actividad compleja de solución de problemas a partir de sus conocimientos precedentes, pero también de inventivas..

(17) CAPÍTULO I. GENERALIDADES SOBRE EL DISEÑO DIGITAL UTILIZANDO FPGAs. 6. En este sentido, según Wakerly: “El diseño digital es ingeniería, e ingeniería es solucionar un problema... En mi experiencia personal sólo entre un 5-10% de los diseños tienen un aporte nuevo, mientras que el resto está formado por módulos característicos o típicos y diseñar, utilizando estos módulos típicos, es mucho más fácil diseñar en estos tiempos que hace 20 ó 10 años atrás. De manera que entre un 50-100% del tiempo de diseño se consume actualmente en la parte nueva del mismo” (Wakerly, 2000 p.2). En términos generales, se puede definir el diseño electrónico digital como el proceso planificado y organizado mediante el cual se implementa un sistema electrónico digital concreto, con vista a solucionar un problema práctico. El diseño es, además de un proceso tecnológico, el modo de actuación de los especialistas de la electrónica y por tanto una habilidad profesional compleja (Barrios, J. P. 2006). El incremento de la complejidad de los sistemas creados por el ser humano, producto del desarrollo tecnológico en diferentes áreas, hizo necesario desarrollar métodos de diseño que garantizaran el correcto funcionamiento de un sistema una vez implementado, así como la eficiencia y la repetibilidad de dicho proceso. Dichos métodos han cambiando conforme se ha elevado la complejidad de los mismos. Numerosos han sido los autores que han propuesto modelos del proceso de diseño, aplicables a cualquier tecnología, que permitan el desarrollo de un método para realizarlo (Mandado, 2000 p. 12). Como rasgo común se concibe la estructura del diseño como un sistema jerárquico en el que cada componente constituye un módulo separado. La utilización de esta estrategia en el diseño de sistemas digitales complejos tiene la ventaja de que los módulos pueden ser realizados para diseñar diferentes sistemas (reutilización), con la consiguiente reducción del costo de diseño. Los sistemas digitales complejos se definen como aquellos compuestos por un número de componentes elementales (compuertas) superior a cien y se caracterizan porque en su diseño no es posible utilizar los métodos manuales “clásicos" (ecuaciones del Álgebra de Boole, relaciones de entrada salida en forma de tabla de verdad, entre otras). Lo anterior permite caracterizar al diseño tanto como resultado (implementación física), como a la vez proceso o sucesión de fases, con un método o estrategia propia. Esta interrelación dialéctica entre contenido y método no es privativa del diseño. Al respecto Lenin (Klingberg, 1980) comentaba en sus Escritos Filosóficos la definición de Hegel sobre método como: “la conciencia sobre la forma.

(18) CAPÍTULO I. GENERALIDADES SOBRE EL DISEÑO DIGITAL UTILIZANDO FPGAs. 7. del movimiento interno propio del contenido”. La anterior definición revela el carácter histórico y subjetivo del método y su dependencia del contenido que, a su vez, está históricamente determinado. A manera de resumen histórico, la tabla I.1 muestra la relación entre el contenido del diseño de los sistemas digitales y los métodos y medios para solucionar el mismo. Según Moreno: “las características más destacadas de las tendencias actuales en diseño de sistemas electrónicos se pueden resumir en un incremento creciente de la complejidad de los sistemas a desarrollar, ciclos de vida y de diseño cada vez más reducidos, así como la necesidad de incluir un cierto grado de flexibilidad que permita afrontar posibles modificaciones o actualizaciones futuras”. (Moreno, 2005 p.5). Para Al-Hadithi y Suardíaz: “La consolidación en la década de los noventa de los lenguajes de descripción de hardware (HDLs, del inglés: Hardware Description Languages) ha supuesto, por otro lado, la implantación progresiva de la denominada metodología de diseño ‘Top-Down’ (descendente) que, en contraposición a la metodología ascendente (Bottom-Up), permiten la descripción del sistema al más alto nivel. Hoy en día los HDLs están ampliamente difundidos y estandarizados bajo la IEEE, por lo que su aprendizaje, más que aconsejable, es una necesidad en la pequeña y gran industria”. (Al-Hadithi y Suardíaz, 2004 p.14). Es importante señalar que los lenguajes de descripción de hardware, al formar parte de las herramientas de ayuda al diseño electrónico por computadora (EDA en inglés), permiten el trabajo en equipo. Así, al estructurar el desarrollo del proyecto, cada integrante del equipo de diseño puede trabajar en subproyectos antes de integrar todas las partes del sistema y establecer una comunicación tecnológica a través de la documentación del subproyecto mediante un lenguaje de descripción de hardware común (Barrios, J. P. 2006). Dicha tendencia se ha generalizado dentro del diseño digital moderno (Sagahyroon, 2000). El trabajo por niveles de jerarquía, la descripción mediante lenguajes de hardware de alto nivel y el uso de herramientas de software en prácticamente en todas las etapas del proceso de diseño, se integran en entornos informáticos favorables al intercambio entre diseñadores y la reutilización de diseños. En el proceso de diseño digital tiene una gran importancia la comunicación y la documentación..

(19) CAPÍTULO I. GENERALIDADES SOBRE EL DISEÑO DIGITAL UTILIZANDO FPGAs. 8. Tabla I.1. Relación histórica entre el contenido del diseño y los métodos y medios empleados. Período 1970. 1980. 1990. 2000. Problemas a Diseñar (Contenido) Métodos y Medios Memorias, Microprocesadores de 8 y Metodología de diseño ascendente 16 bits. (bottom-up). Herramientas de ayuda al diseño muy rudimentarias. Tecnología bipolar y NMOS. Diseño centrado en las fábricas específicas de semiconductores. Diseño de Circuitos Integrados de Se separan los procesos de diseño Aplicación Específica (ASICs), y fabricación. circuitos integrados de alta densidad Metodologías de diseño programables (FPGAs y CPLD), ascendentes (bottom-up) y descendentes microprocesadores de 32 bits y (top-down). procesadores digitales de señales. Surgimiento del lenguaje de descripción de hardware VHDL. Tecnologías CMOS y BiCMOS. Desarrollo de herramientas computacionales de ayuda al diseño. Predominio de los FPGAs y CPLDs Desarrollo profundo de la sobre los ASICs, desarrollo de tecnología CMOS. aplicaciones en un solo chip (System Herramientas computacionales de on a Chip), Sistemas Complejos de ayuda al diseño muy poderosas. Co-diseño Hardware-Software. Diseño Predominio de la metodología de de procesadores Pentium, Interfaces diseño descendente (top-down). para redes y Multimedia. Desarrollo y actualización del VHDL. Abundantes bibliotecas de módulos complejos reutilizables. Desarrollo de Co-Diseño Hardware-Software (Co-Design). Predominio de los System on a Chip Consolidación del Co-Design y la (SoC), Diseños completos en un chip convergencia Hardware-Software. (mixtos), procesadores con propiedad Fortalecimiento de la metodología intelectual. de diseño descendente (top-down). Poderosas herramientas de ayuda al diseño por computadora (CAD-EDA)*. Lenguajes de descripción de hardware con síntesis automatizada. Fuerte independencia entre el diseño y la tecnología. Trabajo en equipo con amplio uso de las TIC. Tecnología submicrónica.. * CAD: Diseño Asistido por Computadora en inglés. EDA: Herramientas de Diseño Electrónico Automatizadas..

(20) CAPÍTULO I. GENERALIDADES SOBRE EL DISEÑO DIGITAL UTILIZANDO FPGAs. 9. I.1.2. Invariantes funcionales de la habilidad diseñar en electrónica digital Una caracterización didáctica de la habilidad diseñar [Barrios, 2006], presupone un análisis de su estructura interna y la determinación de las diferentes acciones y operaciones de esta actividad compleja generalizada. Si bien Wakerly (2000) define diseñar como ingeniería, e ingeniería como resolver un problema, no basta con ver esta actividad en su manifestación externa. Para lograr la generalización de la habilidad diseñar, Barrios [2006] asume como fundamentos metodológicos los relacionados con la teoría de la actividad de la escuela soviética y las experiencias cubanas en el desarrollo de investigaciones relacionadas con la enseñanza basada en problemas para ciencias exactas y/o experimentales aplicando los principios generales de la misma (véase Labarrere, 1996; Rizo & Campistrous, 1998; Llivina, 2000; Leyva, 2002; Rivero, 2002). Dicho autor define la habilidad diseñar, en electrónica digital, como: la actividad mediante la cual se especifica, modela, describe, simula, implementa y comprueba un sistema electrónico digital destinado a resolver, de forma eficiente y en un tiempo adecuado, un problema práctico de la profesión. Como se observa, en su definición se encuentran todos los factores esenciales para el desarrollo de una actividad: ¾. Motivo ó demanda: Resolver un problema práctico.. ¾. Objetivo: Resolver el mismo de forma eficiente.. ¾. Método: Mediante un conjunto de acciones.. En la figura I.1 se muestra lo que [Barrios, 2006] constituye la estructura interna de la habilidad diseñar como actividad compleja generalizada y la interacción entre sus acciones y operaciones. I.2. Definiciones básicas acerca de los lenguajes de descripción de hardware. En general, los HDL son lenguajes de programación, establecidos como normas internacionales que permiten describir, en un ordenador, el funcionamiento de un circuito digital de cualquier nivel de complejidad..

(21) CAPÍTULO I. GENERALIDADES SOBRE EL DISEÑO DIGITAL UTILIZANDO FPGAs. 10. Figura I.1. Estructura interna de la habilidad diseñar. Lo que diferencia los HDL de los lenguajes de programación para computadoras (C, Pascal, Basic, Fortran, etc.) es que mientras que éstos se ejecutan de forma secuencial; los HDL, por simular el funcionamiento de un sistema digital como un todo, se ejecutan simultánea o concurrentemente. El surgimiento de los HDL fue el resultado de un esfuerzo internacional por tener un lenguaje común de intercambio de información de los diseños digitales que permitiera el desarrollo de proyectos en equipo. Dentro de los más difundidos en la actualidad se encuentran el VHDL y el Verilog, ambos normas internacionales de la IEEE (Instituto de Ingenieros Eléctricos y Electrónicos en inglés). El VHDL ó IEEE-1076/87/93 tiene una mayor difusión en el contexto europeo, mientras que el uso del Verilog se encuentra mayormente en Norteamérica y Japón (Pollán, 2004 p. 58; Gadea, 2004 p. 5). Las siglas del VHDL proceden del inglés: Very high speed integrated circuit Hardware Description Language que significan: lenguaje de descripción para hardware de circuitos integrados de alta.

(22) CAPÍTULO I. GENERALIDADES SOBRE EL DISEÑO DIGITAL UTILIZANDO FPGAs. 11. velocidad. Desde su surgimiento en 1987 el mismo ha venido perfeccionándose y ampliándose su utilidad, que inicialmente era para la descripción funcional (sin interesar la implementación física del modelo) y la documentación de los proyectos. Actualmente está integrado en las herramientas de ayuda al diseño por computadora y permite, a partir de esta descripción funcional o de comportamiento (tal y como si se estuviese describiendo en lenguaje natural), la síntesis o compilación automática sobre un circuito integrado digital. Si en sus inicios el diseño electrónico digital implicaba enfrentarse a extensas hojas de esquemas de componentes interconectados que, con el paso del tiempo, se hacían difícil de entender por otros diseñadores ó incluso por él mismo; la utilización actual de los lenguajes HDL permite describir el funcionamiento del sistema bajo diseño en un lenguaje formal, sin ambigüedades y de forma clara. Otra de sus ventajas es que permite la simulación de lo descrito y, por lo tanto, comprobar si el modelo funcional del problema a resolver es adecuado para continuar con las restantes etapas del diseño (Barrios.J.P, 2006). I.2.1. El lenguaje VHDL. Sus ventajas para el diseño de sistemas digitales. Numerosos lenguajes de descripción del hardware han sido desarrollados en los últimos 30 años. Desde el CDL (Computer Design Language), presentado en 1965, hasta el Verilog, desarrollado en 1983-1984. Siempre se han buscado formas cómodas, sencillas y potentes de describir los circuitos electrónicos. Por parte de las empresas que comercializan herramientas de diseño microelectrónico, el lenguaje más conocido hasta principios de los años 90 fue Verilog, propiedad de la compañía Cadence Design Systems, este lenguaje es sencillo de aprender y utilizar, además de poseer gran capacidad de descripción de circuitos digitales, pero existen otros como el VHDL el cual se estandarizó por el Instituto de Ingenieros Eléctricos y Electrónicos (IEEE, por sus siglas en inglés). En 1980 el Departamento de Defensa de Estados Unidos (DoD) inició un proyecto denominado Very High Speed Integrated Circuit (VHSIC), con el principal objetivo de desarrollar circuitos integrados en tecnología de 0,5 micras con muy altas prestaciones y resistencia a la radiación. Estos circuitos se habrían de integrar en los sistemas militares y mejorarlos en gran medida. Antes del término de ese mismo año se hizo evidente que para poder organizar y coordinar el desarrollo de los 28 circuitos integrados propuestos por diversas compañías, era necesario el empleo de un lenguaje de descripción del hardware que permitiera el flujo de información entre diseñadores, fabricantes y usuarios. De esta forma, en otoño de 1980, se iniciaron los trámites para.

(23) CAPÍTULO I. GENERALIDADES SOBRE EL DISEÑO DIGITAL UTILIZANDO FPGAs. 12. el desarrollo de un nuevo lenguaje de descripción denominado VHSIC Hardware Design/Description Language o VHD2L, que posteriormente se simplificaría en el acrónimo VHDL. En julio de 1983 se inició formalmente el proyecto de desarrollo del lenguaje VHDL, con la participación de tres compañías: Intermetrics, Texas Instruments e IBM. La aparición del VHDL provocó un fuerte impulso para que numerosas firmas de herramientas de ayuda al diseño (EDA) comenzaran a incorporar compiladores y simuladores en sus paquetes de diseño. A partir de este momento se pusieron de manifiesto las ventajas de la estandarización, lo que resultó de gran interés para las universidades que harían uso de dicho lenguaje. Las empresas de herramientas de diseño microelectrónico pasaron a incluirlo como parte sus entornos. VHDL permite modelar y simular un sistema desde un alto nivel de abstracción hasta el nivel lógico más elemental con compuertas y biestables. Básicamente permite tres estilos de descripción: algorítmico o de comportamiento, RTL (Register Transfer Level) o flujo de datos y estructural. No obstante, pueden mezclarse en un mismo diseño los distintos estilos de descripción o niveles de abstracción. Los modelos creados pueden ser usados para diferentes tecnologías (reutilización del código). También permite especificar características tecnológicas mediante la definición de nuevos tipos, componentes, atributos y parámetros genéricos. Es un lenguaje normalizado, por lo que es compatible con prácticamente la totalidad de las herramientas de diseño disponibles en el mercado. La normalización implica que no es un lenguaje de propietario, por lo que cualquier usuario puede desarrollar una herramienta para VHDL y comercializarla. Además de ello, este lenguaje puede usarse para la comunicación entre distintas herramientas EDA, por ejemplo, un programa de captura de esquemáticos podría generar una descripción VHDL, que a su vez podría usarse como entrada a un simulador. Permite diseño jerárquico y el diseño top-down, este último incrementa la productividad y eficiencia de los diseños, particularmente de los más complejos, aunque también permite el diseño bottom-up o una combinación de éste y el top-down. Admite diseños arbitrariamente largos, pues no existen limitaciones impuestas al tamaño de los mismos (Dorta, G. 2006). VHDL permite al diseñador concentrarse en la funcionalidad sin tener que dedicar tiempo y esfuerzos a factores que no afectan a la misma. En el diseño tradicional, el diseñador tenía que.

(24) CAPÍTULO I. GENERALIDADES SOBRE EL DISEÑO DIGITAL UTILIZANDO FPGAs. 13. comprobar paralelamente y de forma manual factores puramente tecnológicos como retardos, área, fan-out, etcétera. I.3. Sistema convertidor de datos. Como se puede observar para procesar señales analógicas por medios digitales es necesario convertirlas a formato digital, esto es, transformarlas en una secuencia de números de precisión finita. Este procedimiento se denomina conversión análogo-digital (A/D) y los dispositivos correspondientes conversores A/D. Conceptualmente, se puede ver la conversión A/D como un proceso en tres pasos, los cuales se ilustran en la figura I.2 [Proakis y Manolakis, 1998, p.21]. 1.. Muestreo: conversión de una señal en tiempo continuo a una señal en tiempo discreto.. 2.. Cuantificación: conversión de una señal en tiempo discreto con valores continuos a una señal. en tiempo discreto con valores discretos (señal digital). 3.. Codificación: en este proceso cada valor discreto se representa mediante una secuencia. binaria de b bits.. Figura I.2. Partes básicas de un conversor analógico- digital (A/D). Aunque se puede modelar un conversor A/D como un muestreador seguido de un cuantificador, en la práctica la conversión A/D se efectúa en un único dispositivo que toma la señal analógica y produce un número codificado en binario. Estos dispositivos tienen gran importancia práctica ya que por medio de ellos se pueden digitalizar señales del mundo real para ser almacenadas o introducidas en algún tipo de procesador digital para su posterior procesamiento y/o utilización. I.4. Ventajas que presenta la utilización de FPGAs. Un FPGA es un dispositivo cuyas características pueden ser modificadas, manipuladas o almacenadas mediante programación. La arquitectura de un FPGA consiste en arreglos de múltiples.

(25) CAPÍTULO I. GENERALIDADES SOBRE EL DISEÑO DIGITAL UTILIZANDO FPGAs. 14. celdas lógicas las cuales se comunican unas con otras mediante canales de conexión verticales y horizontales. Cada celda lógica contiene arreglos de compuertas lógicas AND y OR, así como un número definido de registros y multiplexores. Mediante estos recursos es posible implementar funciones matemáticas y de almacenamiento de datos. El uso de FPGA reduce grandemente la disipación de potencia, y proporciona niveles más altos de integración, ventaja que es aprovechada por los diseñadores de equipos portátiles. Además los FPGAs pueden usarse para diseñar sistemas reconfigurables, siendo esto explotado en el campo de las telecomunicaciones cuyo entorno está en constante evolución, por lo requiere de tecnologías de alta flexibilidad. En el mercado actualmente se ofrecen una amplia gama de productos de FPGA, sus principales suministradores son [“FPGA”, 2006]: •. Altera.. •. Atmel.. •. Cypress.. •. Lattice.. •. Xilinx.. Las familias de dispositivos electrónicos de las firmas anteriores, principalmente Altera y Xilinx, ofrecen realces arquitectónicos significativos orientados a DSP sobre dispositivos FPGA en los cuales existe una mejora del rendimiento energético y de su relación costo-funcionamiento. Además, Altera y Xilinx ahora ofrecen ayudas sofisticadas orientadas al desarrollo de DSP, tales como las interfaces a las herramientas de alto nivel de DSP; y utilizan el lenguaje de descripción de hardware VHDL (Very high speed integrated circuit Hardware Description Language) para el diseño e implementación de sistemas digitales, del cual se hace referencia más adelante. Por otra parte, los requisitos de cómputo de usos en telecomunicaciones de hoy, exceden a menudo el funcionamiento disponible de los procesadores más rápidos de DSP. Esto hace que FPGA sea una solución potencialmente atractiva para ciertos usos de DSP, lo cual constituye un desafío dominante para los diseñadores de estos sistemas. En un procesador, la arquitectura y el sistema de instrucción son fijos; los grados de libertad principales al poner una función en ejecución consisten en elegir qué instrucciones se utilizan y cómo.

(26) CAPÍTULO I. GENERALIDADES SOBRE EL DISEÑO DIGITAL UTILIZANDO FPGAs. 15. se piden las mismas. En un FPGA a diferencia de un procesador, los grados de libertad al poner en uso la ejecución DSP son innumerables [Hernández, 2005]. Además dada la gran cantidad de compuertas con las que cuenta un FPGA, es posible implementar sistemas digitales muy complejos, entre los que se destaca el filtrado digital. Por otra parte, en un FPGA es posible realizar modificaciones de último minuto sin que esto implique grandes alteraciones en el hardware o en el software. I.5. Conclusiones parciales del capítulo. A partir del análisis de los contenidos tratados en este capítulo, se derivan las siguientes conclusiones: 1.. El diseño electrónico encierra un modo de actuación y por tanto es una habilidad en los. profesionales de las Telecomunicaciones y la Electrónica. Diseñar es en esencia resolver un problema de la práctica utilizando los conocimientos, los métodos y los componentes y sistemas digitales. 2.. El desarrollo de la electrónica en general y de la electrónica digital, en particular desde 1980,. ha modificado el contenido y los métodos de diseñar. El uso de herramientas computacionales de ayuda al diseño, las estrategias de diseño descendente (top-down), la utilización de los lenguajes de descripción de hardware (HDL) y el trabajo en equipos de proyectos, caracterizan el estado actual de esta ciencia aplicada. 3.. La habilidad diseñar, en Electrónica Digital, se define como: la actividad mediante la que se. especifica, modela, describe, simula, implementa y comprueba un sistema electrónico digital destinado a resolver, de forma eficiente y en un tiempo adecuado, un problema práctico profesional. Diseñar es, además de un proceso tecnológico, el modo de actuación de los especialistas de la electrónica, y constituye por tanto una habilidad profesional compleja. 4.. El uso de FPGA constituye una solución atractiva en la implementación de sistemas digitales. complejos. 5.. El conocimiento del lenguaje VHDL resulta de gran utilidad en el desarrollo de sistemas. electrónicos digitales debido a las ventajas y facilidades que brinda..

(27) CAPÍTULO II PARTICULARIDADES DEL HARDWARE UTILIZADO E INTRODUCCIÓN AL QUARTUS II. 16. CAPÍTULO II PARTICULARIDADES DEL HARDWARE UTILIZADO E INTRODUCCIÓN AL QUARTUS II. II.1. Breve descripción del Conversor A/D (ADC0804LCN). Para el montaje demostrativo del diseño, se necesitará un conversor A/D, por tanto se impone la necesidad de brindar un pequeño compendio de las características técnicas de este dispositivo con que se cuenta. La familia de ADC080X es de tecnología CMOS. El ADC0804 es un conversor de aproximaciones sucesivas que requiere de una señal de reloj para su funcionamiento. El propio conversor dispone de un circuito generador de reloj, cuya frecuencia de oscilación viene fijada por una resistencia y un condensador externos. Entre sus características está la de poseer un voltaje analógico diferencial a la entrada, el cual puede ser utilizado en rangos de voltajes de cero a un valor de entrada analógico definido. Además, la entrada de voltaje de referencia se puede usar para ajustar la codificación manteniendo su resolución. Este dispositivo tiene un total de 20 pines y un ancho estándar de 0.3 pulgadas como se muestra en la Figura II.1. A continuación aparece una tabla donde se presentan otras características que resultan importantes del convertidor en cuestión, las restantes pueden ser consultadas en la siguiente publicación [DATA CONVERSION/ACQUISITION, 1980, p.5-21 – 5-44]. Tabla II.1. Características del convertidor ADC8004. Símbolo Parámetro Mínimo fCLK Frecuencia de reloj 100 Tconv Tiempo de conversión 62 tacc Tiempo de acceso 135 TA Temperatura de trabajo 0 Resolución. Máximo 800 73 200 70 8. Unidades kHz TCLK ns oC bits.

(28) CAPÍTULO II PARTICULARIDADES DEL HARDWARE UTILIZADO E INTRODUCCIÓN AL QUARTUS II. 17. Figura II.1. Distribución de pines del ADC0804. II.2. Características generales de las FPGAs y los CPLDs de la firma Altera. La Familia APEX 20K. II.2.1. Descripción General. Los dispositivos APEXTM 20K son los primeros PLDs (dispositivos lógicos programables) diseñados con la arquitectura MultiCore, los cuales combinan las fortalezas de los dispositivos basados en LUT y en términos de productos con una estructura de memoria enriquecida. LUT (look-up-table)- (mirar sobre su tabla) consiste en: construcción tabular, la forma de configurar funciones booleanas mediante multiplexores, cuyas líneas de entrada reciben los valores de la tabla de verdad de la función que le corresponde al vector de entrada. La lógica basada en LUT mantiene un desempeño optimizado y eficiencia para flujo de datos, registros intensivos, lógica matemática, o diseños con procesamiento de señales digitales. La lógica basada en términos de producto es optimizada para flujos complejos combinacionales, tales como máquinas de estado complejas, LUT y lógica basada en términos de productos, combinada con las funciones de memoria y la extensa variedad de Mega-Core y las funciones AMPP (Altera® Megafunction Partners Program) hacen la arquitectura del dispositivo APEX 20K singularmente cómodo para diseños de sistemas programables en un chip (SoC en inglés)..

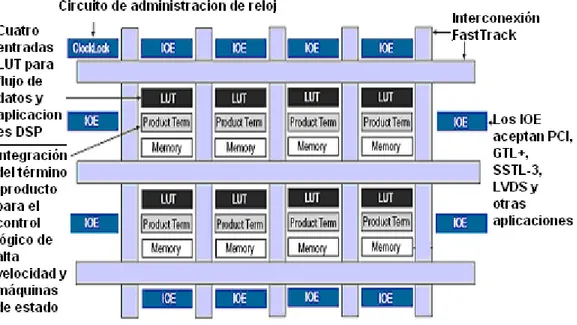

(29) CAPÍTULO II PARTICULARIDADES DEL HARDWARE UTILIZADO E INTRODUCCIÓN AL QUARTUS II. 18. Los dispositivos APEX 20KE son el súper modelo de los dispositivos APEX 20K e incluye características adicionales tales como el soporte avanzado de I/O Standard, CAM (memoria direccionable por contenido), relojes globales adicionales, y circuitería de reloj ClockLock extendida. Además, los dispositivos APEX 20KE extienden la familia APEX 20K a 1.5 millones de compuertas. Los dispositivos APEX 20KE son denotados con un sufijo “E” en el nombre del dispositivo. Todos los dispositivos APEX 20K son reconfigurables y son 100% probados. Los dispositivos APEX 20K pueden ser configurados en la placa para la funcionalidad específica requerida. Los dispositivos APEX 20K son configurados para que enciendan al alimentarse, con almacenamiento de datos en un dispositivo de configuración serie de Altera o provisto por un sistema controlador. Además, los dispositivos APEX 20K contienen una interfase optimizada que permite a los microprocesadores configurar los dispositivos APEX 20K, serie o paralelo y sincrónicamente o asincrónicamente. La interfase también permite a los microprocesadores tratar los dispositivos APEX 20K como memoria y configurar el dispositivo escribiendo a una localización de la memoria virtual, haciendo fácil la reconfiguración. Después de que se haya configurado un dispositivo APEX 20K, puede ser reconfigurado en el circuito reseteando el sistema y cargando el nuevo dato. II.2.2. Descripción funcional. Las interconexiones de señales dentro del dispositivo APEX 20K son proporcionadas por la interconexión FastTrack. Cada pin de entrada-salida es alimentado por un elemento de la entradasalida (IOE) localizado en el final de cada fila y columna de la interconexión FastTrack. Cada IOE contiene un buffer I/O bidireccional y un registro que se puede utilizar como una entrada o registro de salida para alimentar la entrada, la salida, o señales bidireccionales. Cuando es usado con un pin de reloj dedicado, estos registros proporcionan funcionamiento excepcional. Las IOEs proporcionan una variedad de características, tales como 3.3-V, 64-bit, PCI 66-MHz; ayuda de JTAG BST; control de slew-rate; y buffer de tres estados. El ESB puede implementar una variedad de funciones de memoria, incluyendo CAM, RAM, RAM de doble puerto, ROM y funciones FIFO. Embebiendo la memoria directamente dentro del dado se logra eficiencia y reduce el área del dado comparado con las implementaciones de RAM distribuida..

(30) CAPÍTULO II PARTICULARIDADES DEL HARDWARE UTILIZADO E INTRODUCCIÓN AL QUARTUS II. 19. Además, la abundancia de ESBs en cascada asegura que el dispositivo APEX 20K puede implementar múltiples bloques de memoria extendidos para los diseños de alta densidad. Los ESB de alta velocidad aseguran implementar pequeños bloques de memoria sin ninguna penalidad de velocidad. La abundancia de ESBs asegura que los diseñadores puedan crear tantos bloques de memoria de diferentes tamaños como el sistema requiera. Los dispositivos APEX 20K proporcionan dos pines dedicados a reloj y cuatro a entradas que manejan las entradas de control de registro. Estas señales aseguran la distribución eficiente de alta velocidad y señales de control de bajo esquema. Los pines de reloj dedicado en los dispositivos APEX 20K también pueden alimentar lógica. Los dispositivos también proporcionan administración de circuitos de reloj ClockLock y ClockBoost. Los dispositivos APEX 20KE proporcionan dos pines de reloj dedicado adicionales, para un total de cuatro pines de reloj dedicado. La figura II.2 muestra una descripción del diagrama en bloque del dispositivo APEX 20K.. Figura II.2. Diagrama en bloque del dispositivo APEX 20K (Altera, 2006).. II.2.3. Estructura de MegaLAB. Los dispositivos APEX 20K son construidos de una serie de estructuras MegaLABTM. Cada estructura MegaLAB contiene un grupo de bloques de arreglos lógicos (LABs), un ESB, y una interconexión de MegaLAB, que encamina señales dentro de la estructura de MegaLAB. El.

(31) CAPÍTULO II PARTICULARIDADES DEL HARDWARE UTILIZADO E INTRODUCCIÓN AL QUARTUS II. 20. dispositivo EP20K30E tiene 10 LABs, los dispositivos EP20K60E hasta los EP20K600E tienen 16 LABs, y los EP20K1000E hasta EP20K1500E tienen 24 LABs. Las señales son encaminadas entre las estructuras MegaLAB y los pines I/O a través de la interconexión FastTrack. Además, los bordes de los LABs pueden ser manejados por los pines I/O a través de la interconexión local. La figura II.3 muestra la estructura MegaLAB.. Figura II.3. Estructura MegaLAB. II.2.4. Bloque de arreglo lógico. Cada LAB consiste en 10 LEs, el LE asociado lleva y conecta en cascada señales de control de LAB, y la interconexión local. La interconexión local transfiere señales entre LEs en el mismo o adyacentes LABs, IOEs, o ESBs. El compilador de Quartus II implementa lógica asociada dentro de un LAB o los LABs adyacentes, permitiendo el uso de una interconexión local rápida para un alto rendimiento. La figura II.4 muestra el LAB APEX 20K. Los dispositivos APEX 20K utilizan una estructura interpolada de LAB. Esta estructura permite que cada LE conduzca dos áreas locales de la interconexión. Esta característica reduce al mínimo el uso de los MegaLAB y la interconexión FastTrack, proporcionando mayor funcionamiento y flexibilidad. Cada LE puede controlar otros 29 LEs a través de la interconexión local rápida..

(32) CAPÍTULO II PARTICULARIDADES DEL HARDWARE UTILIZADO E INTRODUCCIÓN AL QUARTUS II. 21. Figura II.4. LABs (Altera, 2006). Cada LAB contiene lógica dedicada para manejo de señales de control a sus LEs y ESBs. Las señales de control incluyen: reloj, habilitación de reloj, clear asincrónico, preset asincrónico, carga asincrónica, clear sincrónico, y señales de carga sincrónicas. Un máximo de seis señales de control pueden ser usadas a la vez. Aunque la carga sincrónica y las señales de clear son generalmente usadas cuando se implementan contadores, ellas también pueden ser utilizadas en otras funciones. Cada LAB puede utilizar dos relojes y dos señales de habilitación de reloj. Cada reloj de los LABs y señales de habilitación de reloj son enlazadas (ejemplo, cualquier LE en un LAB particular que utilice CLK1 también utilizará CLKENA1). Los LEs con el mismo reloj pero diferentes señales de habilitación de reloj permiten usar ambas señales de reloj en un LAB o son colocadas en LABs separados. Si los bordes de subida y bajada del reloj se utilizan en un LAB, se usan ambas señales de reloj del LAB extendido..

(33) CAPÍTULO II PARTICULARIDADES DEL HARDWARE UTILIZADO E INTRODUCCIÓN AL QUARTUS II. 22. Las señales de control de LAB extendido pueden ser generadas desde una interconexión local de LAB, señales globales, y pines de reloj dedicados. El bajo esquema inherente de la habilitación de la interconexión FastTrack permite ser utilizada para la distribución del reloj. La figura II.5 muestra el circuito de generación de la señal de control del LAB.. Figura II.5. Circuito de generación de la señal de control del LAB. Nota: 1-. Los dispositivos APEX 20KE tienen cuatro relojes dedicados.. 2-. Las señales LABCLR1 y LABCLR2 controlan también la carga y preset asincrónicos para. LEs dentro del LAB. 3-. La señal SYNCCLR puede ser generada por la interconexión local o señales globales.. II.2.5. Elemento lógico. El LE, la unidad más pequeña de la lógica en la arquitectura APEX 20K, es compacto y proporciona uso eficiente de la lógica. Cada LE contiene cuatro entradas LUT, las cuales son un generador de funciones que pueden implementar rápidamente cualquier función de cuatro variables. Además, cada LE contiene un registro programable y controla la interconexión local, la interconexión de MegaLAB, y las estructuras de encaminamiento de la interconexión de FastTrack. Vea la figura II.6..

(34) CAPÍTULO II PARTICULARIDADES DEL HARDWARE UTILIZADO E INTRODUCCIÓN AL QUARTUS II. 23. Figura II.6. Elemento lógico del APEX 20K (Altera, 2006). El registro programable de cada LE se puede configurar para las operaciones D, T, JK, o SR. El reloj del registro y las señales de control clear pueden ser controlados por las señales globales, los pines de propósito general I/O, o cualquier lógica interna. Para las funciones combinatorias, el registro es realimentado y la salida de los LUT controla las salidas de los LE. Cada LE tiene dos salidas que controlan la estructura de encaminamiento local, el MegaLAB, o la interconexión FastTrack. Cada salida se puede controlar independientemente por los LUT o las salidas de los registros. Por ejemplo, el LUT puede controlar una salida mientras que el registro controla la otra salida. Esta característica, llamada empaquetamiento del registro, mejora la utilización del dispositivo porque el registro y el LUT se pueden utilizar para las funciones no relacionadas. El LE puede también controlar versiones registradas y no registradas de la salida del LUT. La arquitectura APEX 20K proporciona dos tipos de flujos de datos dedicados a alta velocidad que conectan LEs adyacentes sin usar caminos de interconexión local: cadenas de acarreo y cadenas de cascadas. Una cadena de acarreos soporta funciones aritméticas de alta velocidad tales como contadores y sumadores, mientras que en una cadena de cascadas se implementan funciones de.

(35) CAPÍTULO II PARTICULARIDADES DEL HARDWARE UTILIZADO E INTRODUCCIÓN AL QUARTUS II. 24. entradas expandidas tales como comparadores de igualdad con mínimas demoras. Acarreo y cadenas de cascadas conectan los LEs uno con el 10 en un LAB y todos los LABs en la misma estructura de MegaLAB. II.2.6. Modos de operación del LE. El LE APEX 20K puede funcionar en uno de los tres modos siguientes: ■ Modo normal ■ Modo aritmético ■ Modo contador En cada modo, hay siete entradas disponibles al LE (cuatro entradas de datos de la interconexión local del LAB, la realimentación del registro programable, acarreos de entrada y cascadas de entrada del anterior LE) son dirigidos a diferentes destinos para implementar la función lógica deseada. Las señales expandidas de los LAB proporcionan reloj, clear asincrónico, preset asincrónico, carga asincrónica, clear sincrónico, carga sincrónica y control de habilitación de reloj para registro. Estas señales expandidas son validadas en todos los modos LE. El software Quartus II, conjuntamente con funciones parametrizadas tales como LPM (módulo de parámetros lógicos) y funciones de DesignWare, elige automáticamente el modo apropiado para las funciones comunes tales como contadores, sumadores y multiplicadores. Si es requerido, el diseñador puede también crear funciones de propósito especial que especifican cual modo de operación del LE utilizar para un óptimo funcionamiento. La figura II.7 muestra los modos de funcionamiento del LE. II.2.6.1. Modo normal. El modo normal es conveniente para aplicaciones lógicas generales, las funciones combinatorias, o funciones de decodificación que pueden tomar ventaja de las cadenas de cascadas. En modo normal, cuatro entradas de datos de la interconexión local del LAB y el acarreo de entrada son cuatro de las entradas LUT. El compilador del software de Quartus II selecciona automáticamente acarreo de entrada o la señal DATA3 como una de las entradas al LUT. La salida del LUT puede ser combinada con la señal cascada de entrada para formar una cadena de cascadas a través de la señal de salida de la cascada. Los LEs en modo normal soportan empaquetamiento de registros..

(36) CAPÍTULO II PARTICULARIDADES DEL HARDWARE UTILIZADO E INTRODUCCIÓN AL QUARTUS II. 25. Figura II.7. modos de operación del LE del APEX 20K (Altera, 2006). Notas: 1-. Los LEs en modo normal soportan empaquetamiento de registros.. 2-. Hay dos habilitaciones de reloj de LAB expandido por LAB.. 3-. Cuando se usa la entrada de acarreo en modo normal, la característica del empaquetado de. registros queda invalidada. 4-. El multiplexor de la realimentación de registros esta disponible en el LE1 de cada LAB.. 5-. Las señales de entrada DATA1 y DATA2 pueden suministrar habilitación de contador, control de. subida y bajada o señales de realimentación de registro para LEs. 6-. El clear sincrónico y la carga sincrónica del LAB expandido afecta todos los registros en el LAB..

(37) CAPÍTULO II PARTICULARIDADES DEL HARDWARE UTILIZADO E INTRODUCCIÓN AL QUARTUS II. 26. II.2.6.2. Modo aritmético. El modo aritmético es ideal para implementar sumadores, acumuladores, y comparadores. Un LE en modo aritmético utiliza dos 3-entradas LUTs. Un LUT calcula una función de tres entradas, el otro genera una salida de acarreo. Como se muestra en la figura II.7, el primer LUT utiliza la señal acarreo de entrada y dos entradas de datos de la interconexión local del LAB para generar una salida combinatoria o registrada. Por ejemplo, al implementar un sumador, esta salida es la suma de tres señales: DATA1, DATA2, y acarreo de entrada. El segundo LUT utiliza las mismas tres señales para generar la señal acarreo de salida, de este modo creando la cadena de acarreos. El modo aritmético también soporta el uso simultáneo de la cadena de cascadas. El LE en modo aritmético puede manejar versiones de salidas registradas y no registradas de la salida de LUT. El software Quartus II implementa funciones parametrizadas que utilizan el modo aritmético automáticamente cuando sea apropiado; el diseñador no necesita especificar cómo la cadena de acarreos será utilizada. II.2.6.3. Modo contador. El modo contador ofrece habilitación de reloj, habilitación de contador, control de subida y bajada sincrónica y opciones de carga sincrónica. La habilitación de reloj y las señales de control de subida y bajada sincrónica son generadas desde las entradas de datos de la interconexión local del LAB. Las opciones clear sincrónico y carga sincrónica son señales de LAB expandido que afectan todos registros en el LAB. Consecuentemente, si alguno de los LEs en el LAB usa el modo contador, otro LE en ese LAB se debe utilizar como parte del mismo contador, o para una función combinatoria. El software Quartus II ubica automáticamente cualquier registro que no sea utilizado por el contador en otros LABs. El modo contador utiliza dos 3-entrada LUTs: uno genera el contador de datos, y el otro genera el acarreo rápido de bit. Un multiplexor de dos a uno proporciona carga sincrónica, y otra compuerta AND proporciona clear sincrónico. Si la función de cascada es utilizada por un LE en modo contador, el clear o la carga sincrónica elimina cualquier señal de acarreo en la cadena de cascada. El clear sincrónico sustituye la carga sincrónica. Los LEs en modo aritmético pueden controlar las versiones registradas y no registradas de la salida de LUT..

(38) CAPÍTULO II PARTICULARIDADES DEL HARDWARE UTILIZADO E INTRODUCCIÓN AL QUARTUS II. 27. II.2.7. Lógica de Término-Producto. La parte del Término-Producto (The product-term portion) de la arquitectura MultiCore es implementada con el ESB. El ESB se puede configurar para actuar como bloque de macroceldas en un ESB por ESB básico. Cada ESB es alimentado por 32 entradas de la interconexión local adyacente; por lo tanto, puede ser controlado por la interconexión de MegaLAB o de LAB adyacente. También, nueve macroceldas de ESB son realimentadas dentro del ESB a través de la interconexión local para un rendimiento más alto. Los pines dedicados del reloj, las señales globales, y las entradas adicionales de la interconexión local controlan las señales de control de ESB. En modo del Término-Producto, cada ESB contiene 16 macroceldas. Cada macrocelda consiste en dos términos de producto y un registro programable. La figura II.8 muestra el ESB en modo de Término-Producto.. Figura II.8 Lógica termino-producto en ESB. Nota: Los dispositivos APEX 20KE tienen cuatro relojes dedicados. I.2.8. Bloque de sistema embebido (ESB). El ESB puede implementar varios tipos de bloques de memoria, incluyendo bloques dual-port RAM, ROM, FIFO y CAM. El ESB incluye registros de entrada y salida; los registros de entrada sincronizan la escritura, y los registros de salida pueden canalizar diseños para mejorar funcionamiento del.

(39) CAPÍTULO II PARTICULARIDADES DEL HARDWARE UTILIZADO E INTRODUCCIÓN AL QUARTUS II. 28. sistema. El ESB ofrece un modo dual-port, el cual soporta simultáneas lecturas y escrituras en dos diferentes frecuencias de reloj. La figura II.9 muestra el diagrama del bloque ESB.. Figura II.9. diagrama del bloque ESB. Los ESBs pueden implementar RAM sincrónica, la cual es más fácil de utilizar que la RAM asincrónica. Las entradas de ESB son controladas por la interconexión local adyacente, que alternadamente se puede controlar por la interconexión de MegaLAB o de FastTrack. El ESB puede ser controlado por la interconexión local, o un LE adyacente puede controlarlo directamente para el rápido acceso a memoria. Las salidas de ESB controlan el MegaLAB y la interconexión FastTrack. Además, de las diez salidas de ESB, nueve son solamente líneas de salida, controlan la interconexión local para la conexión rápida a los LEs adyacentes o para la rápida realimentación de la lógica término-producto. Cuando implementamos memorias, cada ESB se puede configurar en alguno de los tamaños siguientes: 128 × 16, 256 × 8, 512 × 4, 1.024 × 2, o 2.048 × 1. Combinando múltiples ESBs, el software Quartus II implementa los mayores bloques de memoria automáticamente. El funcionamiento de la memoria no se degrada para bloques de memoria hasta 2.048 palabras enterradas. Cada ESB puede implementar una memoria de 2.048 palabras enterradas. El ESBs se utiliza en paralelo, eliminando de la necesidad de cualquier lógica de control externa y de su retraso asociado. Para crear un bloque de memoria de alta velocidad que sea mayor que 2.048 palabras enterradas, los ESBs controlan líneas de tres estados. Cada línea de tres estados conecta todos los ESBs en una columna de las estructuras MegaLAB y a través de la columna controla la interconexión de MegaLAB y la fila y columna de la interconexión FastTrack. Cada ESB incorpora un decodificador programable para activar apropiadamente el controlador de tres estados. Por ejemplo, para implementar memorias de 8.192 palabras enterradas, se utilizan cuatro ESBs. Once líneas de dirección controlan la memoria de ESB y dos más el decodificador de tres estados. Dependiendo de.

(40) CAPÍTULO II PARTICULARIDADES DEL HARDWARE UTILIZADO E INTRODUCCIÓN AL QUARTUS II. 29. cuál de las páginas de memoria de 2.048 palabras es seleccionada, el controlador apropiado de ESB es encendido, controlando la salida de la línea de tres estados. El software de Quartus II automáticamente combina los ESBs con las líneas de tres estados para formar bloques de memoria “enterrados” (deeper memory blocks) que permiten la interconectividad, de una forma rápida, de los diferentes LABs. La lógica interna de control de tres estados se diseña para evitar contenciones internas y líneas flotando. Vea la figura II.10.. Figura II.10. Bloques de memoria “enterrados” implementados con múltiples ESB (Altera, 2006). El ESB implementa dos formas de memoria dual-port: modo de reloj de lectura-escritura y modo de reloj de entrada-salida. El ESB se puede también utilizar para los usos bidireccionales, aplicaciones de memoria dual-port en los cuales dos puertos leen o escriben simultáneamente. Para implementar este tipo de memoria dual-port, dos o cuatro ESBs se utilizan para apoyar dos lecturas o escrituras simultáneas. Esta funcionalidad se muestra en la figura II.11..

(41) CAPÍTULO II PARTICULARIDADES DEL HARDWARE UTILIZADO E INTRODUCCIÓN AL QUARTUS II. 30. Figura II.11. ESB del APEX 20K implementando dual-port RAM. I.2.9. Interfase multivolt I/O. La arquitectura del dispositivo APEX soporta interfase multivolt I/O, los cuales permiten que los dispositivos APEX en todos los empaquetamientos se comuniquen con sistemas de diferentes fuentes de voltajes. Los dispositivos tienen un grupo de pines a VCC para operaciones internas y buffers de entrada (VCCINT) y otro conjunto para los controladores de las salidas I/O. Los pines VCCINT de APEX 20K siempre deben ser conectados a una fuente de alimentación de 2.5v. Con el nivel de VCCINT de 2.5v los pines de entradas son tolerantes a 2.5v, 3.3v y 5.0v. Los pines VCCIO pueden ser conectados a una fuente de alimentación de 2.5v o 3.3v, dependiendo de los requerimientos de salida. Cuando los pines VCCIO son conectados a una fuente de alimentación de 2.5v, los niveles de salida son compatibles con sistemas de 2.5v. Cuando los pines VCCIO son conectados a Fuentes de alimentación de 3.3v, las salidas en alto son compatibles con sistemas de 3.3v o 5.0v. Tabla II.2: Resumen de tolerancias multivolt I/O que soportan los dispositivos APEX 20K (Altera, 2006)..

Figure

Documento similar

Abstract: This paper reviews the dialogue and controversies between the paratexts of a corpus of collections of short novels –and romances– publi- shed from 1624 to 1637:

Por lo tanto, en base a su perfil de eficacia y seguridad, ofatumumab debe considerarse una alternativa de tratamiento para pacientes con EMRR o EMSP con enfermedad activa

The part I assessment is coordinated involving all MSCs and led by the RMS who prepares a draft assessment report, sends the request for information (RFI) with considerations,

o Si dispone en su establecimiento de alguna silla de ruedas Jazz S50 o 708D cuyo nº de serie figura en el anexo 1 de esta nota informativa, consulte la nota de aviso de la

El diseño es realizado usando el lenguaje Verilog (lenguaje para descripción de hardware) y luego implementado en un FPGA. Sus resultados muestran que su diseño

Ciaurriz quien, durante su primer arlo de estancia en Loyola 40 , catalogó sus fondos siguiendo la división previa a la que nos hemos referido; y si esta labor fue de

Este mismo régimen de deberes tiene sentido cuando la actuación de reforma o renovación significa un cambio radical de la morfología urbana, normalmente acompa- ñado por un cambio

Este curso se ha diseñado especialmente para guiar a los tutores clínicos de Medicina Intensiva en proporcionar un feedback, estructurado y.. efectivo, a los residentes durante