ÍNDICE

Número Tema Página

Objetivo general. I

Objetivos Específicos. I

Justificación. II

1 CAPÍTULO I: Introducción y evolución de los sistemas de comunicación móviles

1.1 Introducción. 1

1.2 Primera generación. 3

1.3 Segunda generación. 5

1.4 Generación 2.5. 7

1.5 Tercera generación. 8

1.6 Cuarta generación. 10

2 CAPÍTULO II: Radio definido por software

2.1 Introducción. 12

2.2 Radio definido por software. 12

2.2.1 Arquitectura de Transmisiones de Radio Tradicional. 13

2.2.2 Arquitectura Ideal de Transmisores de Radio Basados en Software. 14

2.2.3 Principio de Funcionamiento de un Receptor RDS. 16

2.2.4 Conversión de Frecuencia. 17

2.3 Modulación. 17

2.3.1 Tipos de Modulación Analógica y Digital. 18

2.3.2 Demodulación. 20

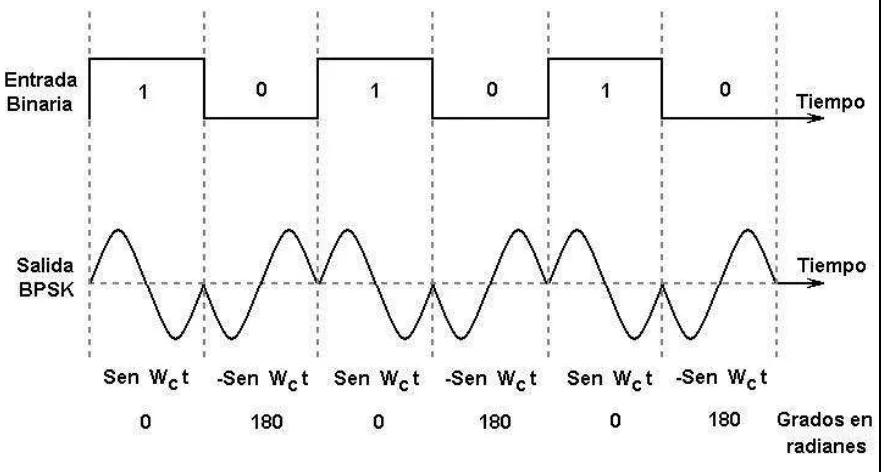

2.4 Transmisión por Desplazamiento de Fase Binaria (BPSK). 20

2.4.1 Transmisor BPSK. 20

2.4.2 Receptor BPSK. 22

2.5 Codificación. 23

2.5.1 Códigos de Paridad. 23

2.5.2 Códigos m entre n. 23

2.6 Códigos de Bloque Lineales Sistemáticos. 24

2.7 Código de Hamming. 27

2.8 Decodificación Hamming. 29

2.9 Códigos Convolucionales. 30

3 CAPÍTULO III: Dispositivos de lógica programable

3.1 Introducción. 31

3.2 PLDs (Programmable Logic Devices). 32

3.3 ASPLDs (Application Specific Programmable Logic Devices). 33

3.4 PAL (Programmable Array Logic). 33

Número Tema Página

3.5.1 Estructura General de la FPGA. 35

3.5.2 Lenguajes para programar en fpgas. 37

4 CAPÍTULO IV: Simulación e implementación en fpga

4.1 Introducción. 41

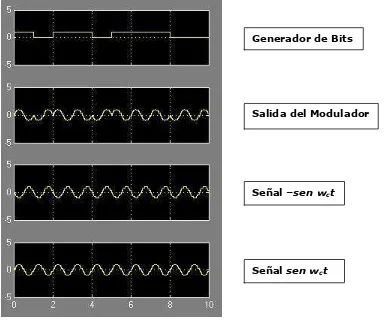

4.2 Modulador BPSK. 41

4.3 Demodulador BPSK. 44

4.4 Codificador Hamming 7,4. 45

4.5 Decodificador Hamming 7,4. 47

4.6 Generar Proyecto ISE para grabar la tarjeta FPGA. 54

4.7 Grabación de la tarjeta FPGA. 56

Conclusiones 64

Recomendaciones para trabajos futuros 64

Glosario 65

Apéndice A 67

Apéndice B 68

Número Tema Página

ÍNDICE DE TABLAS

CAPÍTULO I

1.1 Rangos de frecuencias a las que se trabajaban para eliminar interferencias que llegaran a surgir. 2

1.2 Características de la primera generación. 5

1.3 Características de la segunda generación. 7

1.4 Los principales estándares de comunicación móvil y su evolución de cada uno. 10

CAPÍTULO IV

4.1 Tabla para determinar las salidas trt dependiendo el número de error 50

ÍNDICE DE FIGURAS

CAPÍTULO I

1.1

Figura 1.1 Áreas en formas hexagonales, con su estación móvil y los usuarios que se encuentra adentro de cada una

de ellas. 3

CAPÍTULO II

2.1 Arquitectura Tradicional de Transmisores de Radio. 13

2.2 Arquitectura ideal de Transmisores de Radio Basados en Software. 15

2.3 Combinación de dos señales (fa y fo) mediante un mezclador. 17

2.4 Ejemplo de Modulación. 18

2.5 Gráficas de la modulación en amplitud y en frecuencia. 19

2.6 Demodulación. 20

2.7 Diagrama de un Transmisor BPSK. 21

2.8 Diagrama Fasorial y de Constelación del Modulador BPSK. 21

2.9 Fase de salida contra la relación de tiempo para una forma de onda BPSK. 22

2.10 Diagrama de un Receptor BPSK. 23

CAPÍTULO III

3.1 Estructura interna de un PLD. 32

3.2 Estructura interna de un PAL. 34

3.3 Estructura interna de una FPGA. 36

3.4 Estructura del LUT de un bloque lógico. 37

3.5 Programación de una tarjeta FPGA a pasos. 38

3.6 Tarjeta FPGA Xilinx Spartan-3 200000-puerta. 39

CAPÍTULO IV

4.1 Fase de salida contra la relación de tiempo para una forma de onda BPSK. 41

4.2 Diagrama del modulador BPSK. 42

4.3 Subsistema generador de bits. 42

Número Tema Página

4.5 Diagrama del demodulador BPSK. 44

4.6 Resultados obtenidos del demodulador BPSK. 44

4.7 Diagrama del codificador implementado con compuertas AND y XOR. 46

4.8 Bloque de entrada y salida del codificador. 46

4.9 Subsistema generador de bits. 47

4.10 Resultado obtenido de la simulación del codificador. 47

4.11 Esquema del decodificador hamming. 48

4.12 Subsistema Hamming Decoder. 48

4.13 Diagrama del subsistema syndrome implementado con compuertas AND y XOR. 49

4.14 Entradas y salidas del subsistema syndrome para obtener el número de errores. 50

4.15 Diagrama del subsistema Err loc implementado con compuertas AND y NOT. 51

4.16 Entradas y salidas del subsistema Err loc. 52

4.17

Diagrama de la decodificación, el mensaje original sale por Out2 y los bits de paridad que se le quitan al mensaje por

Out1. 52

4.18 Mensaje codificado. 53

4.19 Resultado obtenido de la simulación del decodificador el mensaje original se muestra por el display2. 53

4.20 Ventana del bloque System Generator para crear proyecto ISE. 54

4.21 Ventana del bloque System Generator generando proyecto ISE. 55

4.22 Archivos generados por System Genrator. 55

4.23 Tarjeta FPGA Spartan 3 Starter Kit. 56

4.24 Conexión del cable JTAG. 56

4.25 Entorno Xilinx ISE. 57

4.26 Ventana del código VHD generado por system generator. 58

4.27 Ventana Xilinx PACE. 59

4.28 Ventana Process Properties – Startup Options. 60

4.29 Ventana iMPACT. 60

4.30 Abriendo el archivo .bit que se va a grabar en el FPGA. 61

4.31 Después de cargar el archivo .bit se abre otra ventana para seleccionar otro archivo. 62

4.32 Ventana Device Programming Properties. 62

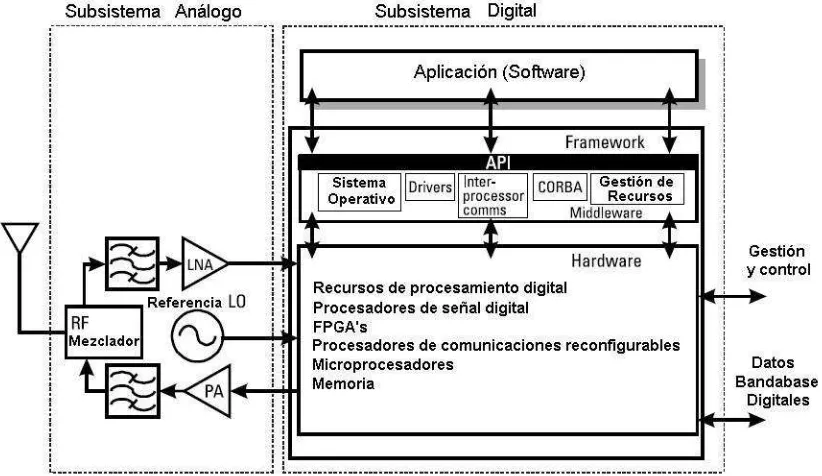

[image:22.612.96.507.76.314.2]

15

Figura 2.2. Arquitectura ideal de Transmisores de Radio Basados en Software.

La arquitectura empuja la etapa de conversión analógica hacia la

derecha lo más cerca posible de la antena, en este caso se prioriza al

amplificador de potencia (PA) en el transmisor y después al amplificador

de bajo ruido (LNA) en el receptor. La separación de portadoras y la

conversión de frecuencias altas y bajas a banda base es mejorada por

los medios de procesamiento digital. De igual manera la codificación del

canal y las funciones de modulación son mejoradas digitalmente en

banda base por los mismos medios de procesamiento. El software para

una arquitectura ideal es en capas entonces el hardware es

completamente abstracto de la aplicación de software. Una capa

intermedia logra esa funcionalidad cubriendo los elementos del

hardware como objetos y proveyendo servicios que permiten a los

objetos comunicarse unos con otros mediante interfases estándar, por

ejemplo Common Object Request Broker Architecture (CORBA). La capa

intermedia incluye: sistema operativo, controladores del hardware,

recursos de administración y otras aplicaciones no específicas de

software. La combinación del hardware y la capa intermedia

frecuentemente se llama framework.

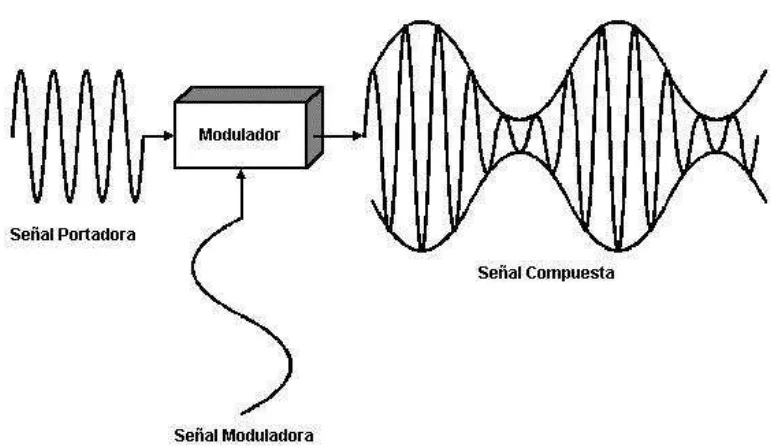

[image:25.612.118.508.95.319.2]

18

Figura 2.4. Ejemplo de Modulación.

Existen varios motivos por los que se modula una señal:

Para facilitar la propagación de la señal de información ya sea por

medios alámbricos o inalámbricos.

Ordena el radioespectro, distribuyendo canales a cada tipo de

información.

Disminuye dimensiones de antenas.

Optimiza el ancho de banda de cada canal.

Evita interferencias entre canales.

Protege la información contra degradaciones por ruido.

Define la calidad de la información transmitida [11].

2.3.1 TIPOS DE MODULACIÓN ANALÓGICA Y DIGITAL

Existen 2 tipos de modulación básicas; la analógica que se realiza a

partir de señales de información como: la voz, audio y video en su

forma eléctrica y la modulación digital que se realiza a partir de señales

generadas por fuentes digitales como una PC.

19

Tipos de modulación digital: Modulación en Amplitud, Apagado

Encendido (ASK), Modulación por Desviación de Frecuencia (FSK),

Modulación por Desviación de Fase (PSK), Modulación de Amplitud en

Cuadratura (QAM) [11].

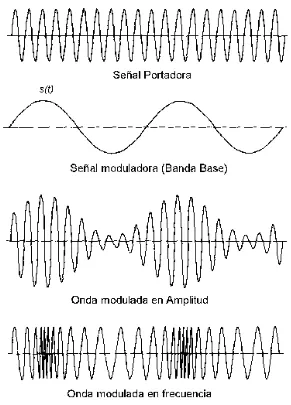

[image:26.612.180.471.200.605.2]

En la figura 2.5 se observa las gráficas de la modulación en amplitud y

en frecuencia.

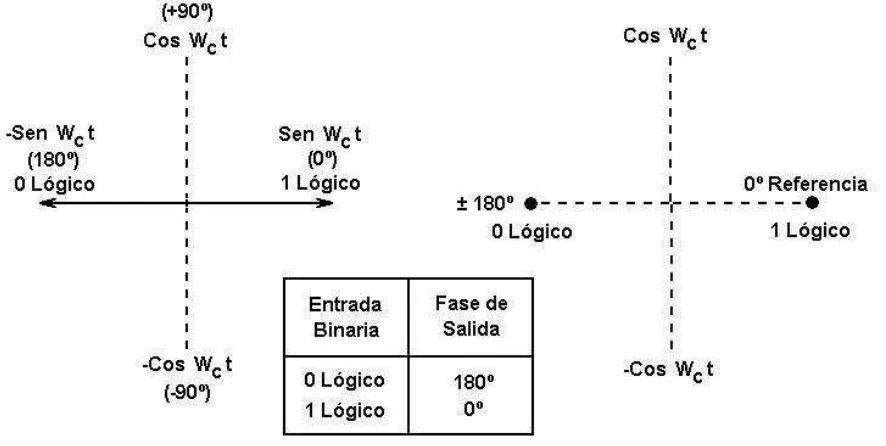

[image:28.612.87.530.359.582.2]

21

Figura 2.7. Diagrama de un Transmisor BPSK.

En la figura 2.8 se muestra el diagrama fasorial y el diagrama de

constelación o diagrama de espacio de estado de señal del modulador

BPSK.

Figura 2.8. Diagrama Fasorial y de Constelación del Modulador BPSK.

32

-

FPIC (Field Programmable Integrated Circuits)

Son chips que se programan por el usuario mediante programadores

comerciales, el término FPIC también incluye a los CI no destinados a

las aplicaciones lógicas, tienen aplicaciones de bajo costo y se clasifican

en PLD (Programmable Logic Device), las FPGA (Field Programmable

Gate Array) y los ASPLD (Aplication Specific Programmable Logic

Devices).

3.2 PLD

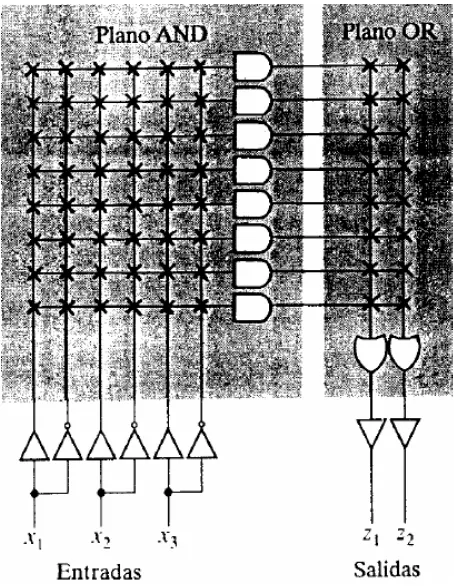

[image:39.612.193.420.346.639.2]

Los PLDs (Programmable Logic Devices) son pequeñas ASICs

configurables por el usuario capaces de realizar una determinada

función lógica. La mayoría de los PLD consisten en una matriz de

puertas AND seguida de otra matriz de puertas OR como se muestra en

la figura 3.1. Mediante esta estructura, puede realizarse cualquier

función como suma de términos productos.

Figura 3.1. Estructura interna de un PLD.

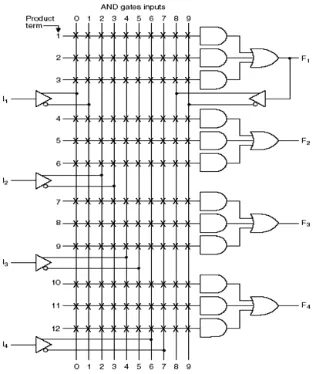

[image:41.612.148.461.68.442.2]

34

Figura 3.2. Estructura interna de una PAL.

3.5 FPGA

La FPGA (Field Programmable Gate Array) es un dispositivo que surgió a

mediados de los ochentas, fue una de las nuevas arquitecturas de los

circuitos integrados, ha sido consideraba como un circuito de lógica

programable.

Este dispositivo ayuda a los diseñadores de sistemas, a revolucionar la

implementación de sistemas digitales configurables ya que permite

manejar y modificar miles de compuertas lógicas que la componen de

esta forma ayuda a evolucionar y mejorar el funcionamiento de otros

sistemas electrónicos de control y de comunicaciones. En este capítulo

hablaremos sobre estas tarjetas.

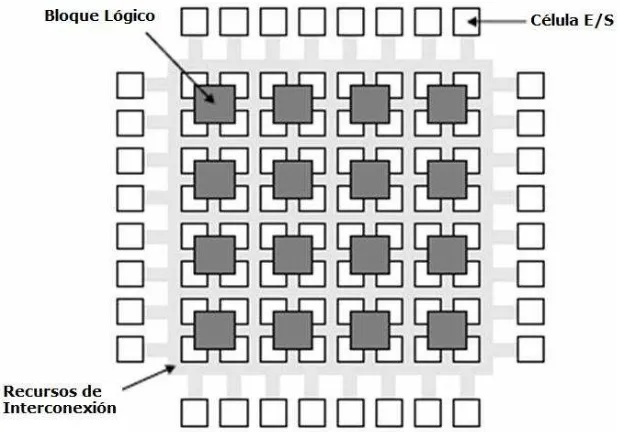

[image:43.612.152.462.70.286.2]

36

Figura 3.3. Estructura interna de una FPGA general

En la figura 3.3 se muestran los elementos básicos que contiene una

FPGA que son los siguientes:

-

Las células de entrada y salida.

-

Recursos de interconexión, cuya estructura y contenido se

denomina arquitectura de rutado.

-

Los bloques lógicos, los componentes que disponen cada uno

pueden variar de acuerdo al fabricante.

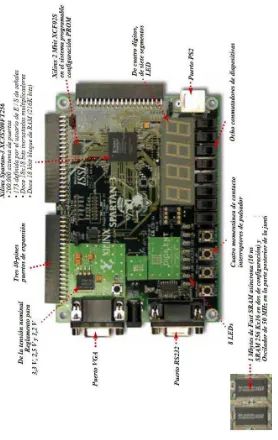

39

Utilizamos las FPGA ya que es una clase especial de chip para

implementar en hardware un código de aplicación, es como tener una

placa para implementar circuitería personalizada por medio de

hardware.

Para este proyecto estamos trabajando con la tarjeta Xilinx Spartan-3

200000-puerta Plataforma FPGA - XC3S200 como se muestra en la

figura 3.6.

[image:46.612.171.449.214.654.2]

41

CAPÍTULO IV: Simulación e implementación en FPGA,

pruebas y resultados.

4.1 INTRODUCCIÓN

En este capítulo se presenta el proceso de diseño, simulación e

implementación del Modulador, Demodulador BPSK, Codificador y

Decodificador Hamming 7,4. El entorno de desarrollo utilizado para

realizar la simulación es Simulink de Mathworks, además de

herramientas de Xilinx como System Generator para realizar los

diagramas a bloques, y Xilinx ISE para grabar la tarjeta FPGA Spartan-3

Starter Kit Board.

4.2 MODULADOR BPSK.

Como ya se ha mencionado en el capítulo 2, la modulación BPSK es una

modulación digital, por lo tanto trabaja con una señal de entrada digital

binaria y tiene 2 fases de salida dependiendo el estado de la señal de

entrada, cuando se tiene un estado alto “1” la portadora se transfiere a

la salida en fase y si es un estado bajo “0” se transfiere desfasada 180º.

[image:48.612.87.529.403.639.2]

En la figura 4.1 se muestra como se realiza la modulación.