Desarrollo de aplicaciones utilizando System Generator y su implementación en un FPGA de Xilinx

Texto completo

(2) Universidad Central “Marta Abreu” de Las Villas Facultad de Ingeniería Eléctrica Departamento de Telecomunicaciones y Electrónica. TRABAJO DE DIPLOMA Desarrollo de aplicaciones utilizando System Generator y su implementación en un FPGA de Xilinx. Autor: Yadir Rodríguez Hernández E-mail: yadirr@uclv.edu.cu. Tutor: Ing. Yakdiel Rodríguez-Gallo Guerra Prof. Instructor Dpto. de Electrónica Facultad de Ing. Eléctrica, UCLV. E-mail: yrodriguez-gallo@uclv.edu.cu Santa Clara 2012 "Año 54 de la Revolución".

(3) Hago constar que el presente trabajo de diploma fue realizado en la Universidad Central “Marta Abreu” de Las Villas como parte de la culminación de estudios de la especialidad de Ingeniería en Telecomunicaciones y Electrónica, autorizando a que el mismo sea utilizado por la Institución, para los fines que estime conveniente, tanto de forma parcial como total y que además no podrá ser presentado en eventos, ni publicados sin autorización de la Universidad.. Firma del Autor Los abajo firmantes certificamos que el presente trabajo ha sido realizado según acuerdo de la dirección de nuestro centro y el mismo cumple con los requisitos que debe tener un trabajo de esta envergadura referido a la temática señalada.. Firma del Autor. Firma del Jefe de Departamento donde se defiende el trabajo. Firma del Responsable de Información Científico-Técnica.

(4) i. PENSAMIENTO. “Hay una fuerza motriz más poderosa que el vapor,. la electricidad y la energía atómica: la voluntad” Albert Einstein.

(5) ii. DEDICATORIA. A mis padres y hermana A Milexy.

(6) iii. AGRADECIMIENTOS. A mis padres y hermana, por haberme apoyado, querido y convertido en la persona que soy. A mi novia Milexy, por llenarme de felicidad. A mi tutor, por su ayuda y dedicación en la elaboración de este trabajo. A mis suegros Maricela y Miguel, por su apoyo en estos años de estudio. A mis compañeros de aula, especialmente a Fontaine y a Héctor. A los profesores y todas las personas que han contribuido a mi formación.. Muchas Gracias.

(7) iv. TAREA TÉCNICA. Para confeccionar el presente trabajo y alcanzar los resultados esperados, fue necesario elaborar las tareas técnicas siguientes:. Caracterización de los FPGAs de Xilinx y de la herramienta System Generator para la implementación de aplicaciones. Realización de una investigación para determinar los principales campos de aplicación en los que se utiliza el software System Generator. Confección de aplicaciones utilizando la herramienta de simulación System Generator. Comprobación del funcionamiento de las aplicaciones en Simulink y en un FPGA de Xilinx. Elaboración del informe final del Trabajo de Diploma.. Firma del Autor. Firma del Tutor.

(8) v. RESUMEN. La presente investigación se dedica al desarrollo de aplicaciones utilizando el software System Generator y a su implementación en un FPGA Spartan-3E de Xilinx. Para ello, se caracterizó la arquitectura básica de los FPGAs, específicamente los desarrollados por Xilinx, y también el software System Generator, identificándose los principales campos en que se utiliza esta herramienta en el mundo. Como resultado de la investigación se confeccionaron tres aplicaciones que muestran el trabajo con este software. Para comprobar el funcionamiento de las aplicaciones desarrolladas se implementaron en el kit Nexys2 disponible en la Facultad. Con la realización de este trabajo se llegó a la conclusión de que System Generator es un software muy versátil para la implementación de complejos sistemas digitales de forma rápida y eficiente..

(9) vi. ÍNDICE. PENSAMIENTO .....................................................................................................................i DEDICATORIA .................................................................................................................... ii AGRADECIMIENTOS ........................................................................................................ iii TAREA TÉCNICA ................................................................................................................iv RESUMEN ............................................................................................................................. v INTRODUCCIÓN .................................................................................................................. 1 CAPÍTULO 1.. CARACTERIZACIÓN DE LOS FPGAS DE XILINX Y DEL. SOFTWARE SYSTEM GENERATOR ................................................................................. 5 1.1. Los FPGAs de Xilinx: evolución y funcionamiento ................................................ 5. 1.1.1. Arquitectura básica de los FPGAs .................................................................... 7. 1.1.2. Kit de desarrollo Nexys2 .................................................................................. 9. 1.2. Características del software System Generator ...................................................... 10. 1.3. Principales campos de aplicación del software System Generator ........................ 14. 1.4. Conclusiones del capítulo ...................................................................................... 19. CAPÍTULO 2.. APLICACIONES. DESARROLLADAS. UTILIZANDO. SYSTEM. GENERATOR ….... ............................................................................................................. 20 2.1. Confección de un cronómetro digital ..................................................................... 20. 2.1.1 2.2. Implementación en la herramienta de simulación .......................................... 22. Confección de un controlador VGA ...................................................................... 24.

(10) vii 2.2.1 2.3. Implementación en la herramienta de simulación .......................................... 27. Confección de un modulador y demodulador 16QAM .......................................... 28. 2.3.1. Características del modulador ......................................................................... 29. 2.3.2. Características del demodulador ..................................................................... 30. 2.3.3. Implementación en la herramienta de simulación .......................................... 32. 2.4. Conclusiones del capítulo ...................................................................................... 33. CAPÍTULO 3.. IMPLEMENTACIÓN Y COMPROBACIÓN DE LAS APLICACIONES ................................................................................................................. 34. 3.1. Implementación en el FPGA de las aplicaciones confeccionadas ......................... 34. 3.1.1 3.2. Descarga del fichero de configuración ........................................................... 35. Evaluación del comportamiento de las aplicaciones .............................................. 35. 3.2.1. Cronómetro digital .......................................................................................... 35. 3.2.2. Controlador VGA ........................................................................................... 38. 3.2.3. Modulador y demodulador 16QAM ............................................................... 41. 3.3. Conclusiones del capítulo ...................................................................................... 46. CONCLUSIONES Y RECOMENDACIONES ................................................................... 47 Conclusiones ..................................................................................................................... 47 Recomendaciones ............................................................................................................. 48 REFERENCIAS BIBLIOGRÁFICAS ................................................................................. 49 ANEXOS .............................................................................................................................. 52 Anexo I. Recomendaciones y requerimientos de hardware y software del sistema para. la instalación del software System Generator ................................................................... 52 Anexo II. Asignación de terminales para las aplicaciones desarrolladas .................... 54.

(11) INTRODUCCIÓN. 1. INTRODUCCIÓN. El desarrollo de nuevas tecnologías de fabricación de circuitos integrados como los FPGAs (Field Programmable Gate Array) durante las últimas décadas, unido a la imperiosa demanda del mercado de la electrónica, ha propiciado la aparición de herramientas de diseño y simulación de dispositivos electrónicos cada vez más potentes y avanzadas, dotadas de capacidades de desarrollo que posibilitan la transformación de una idea inicial, en un diseño final de forma rápida, eficiente, fiable y con un bajo costo asociado. El uso de herramientas de alto nivel para el diseño de hardware permite un mayor nivel de abstracción y una mayor interacción con el diseñador. Generalmente, son más fáciles de aprender pues se separan más del nivel de hardware para ser más claras y sencillas al usuario, lo que posibilita la creación de nuevos dispositivos con una complejidad y funcionalidad mayor. Algunas compañías fabricantes de FPGAs realizan grandes esfuerzos en el desarrollo de herramientas que faciliten la implementación de sistemas complejos en sus dispositivos. Un ejemplo de ello es Xilinx con el desarrollo del software System Generator. System Generator es una herramienta de alto nivel que se integra a Matlab/Simulink para el diseño, simulación e implementación de circuitos en FPGAs. Matlab es un programa de cálculo numérico y visualización de datos para la resolución de problemas complejos planteados en la realización y aplicación de modelos matemáticos de ingeniería. Matlab dispone de herramientas adicionales que expanden sus prestaciones como Simulink, un software para modelar, simular y analizar sistemas dinámicos, el cual proporciona una interfaz de usuario gráfica para construir los modelos como diagramas de bloques. La integración de System Generator con Simulink permite manejar un nivel de abstracción elevado y proporciona un entorno gráfico que facilita la descripción del algoritmo que se va.

(12) INTRODUCCIÓN. 2. a implementar. Una vez verificada la funcionalidad del diseño utilizando las distintas facilidades de generación y visualización de señales proporcionadas por Matlab/Simulink, System Generator lo traslada de forma automática en una implementación hardware, optimizada en términos de área y velocidad. Hasta la fecha no puede considerarse como un sustituto de los lenguajes de descripción de hardware, pero sí un potente complemento. Las posibilidades de este software de diseño, su flexibilidad y su compatibilidad con un gran número de FPGAs y herramientas de Xilinx, hace que su uso en la actualidad se extienda a diversos campos de la electrónica y las telecomunicaciones. Sus facilidades para el procesamiento digital de señales son aprovechadas por especialistas para desarrollar y probar algoritmos para el procesamiento de imágenes. Investigaciones actuales en el mundo de las comunicaciones centran su uso en el desarrollo de etapas de codificación y modulación en sistemas de radio definido por software y en la implementación de la capa física de algunos estándares de redes inalámbricas. En la Facultad de Ingeniería Eléctrica de la Universidad Central “Marta Abreu” de Las Villas se han realizado trabajos de diploma anteriores sobre la tecnología FPGA. En los mismos se evidencian las utilidades que ofrecen los dispositivos de Xilinx y en especial las tarjetas prototipo o kits de desarrollo, con las cuales se pueden implementar diversas aplicaciones. En esas investigaciones se muestra la metodología a seguir para el desarrollo de aplicaciones haciendo uso de la herramienta de software Xilinx ISE, donde la descripción del circuito se realiza mediante esquemáticos, diagramas de estado o lenguajes de descripción de hardware como VHDL (VHSIC Hardware Description Language, donde VHSIC es el acrónimo de Very High Speed Integrated Circuit). Sin embargo, no se ha realizado ningún trabajo que exponga los principales campos de aplicación del software System Generator, las prestaciones que brinda esta herramienta, ni se han desarrollado aplicaciones que muestren el trabajo con la misma. De ahí la importancia que tiene la realización de este trabajo desde el punto de vista tanto teórico como práctico para la Facultad y para aquellas personas que se inicien en el desarrollo de aplicaciones con este software..

(13) INTRODUCCIÓN. 3. Teniendo en cuenta lo anterior, el presente trabajo de diploma plantea el siguiente problema de investigación: ¿Cómo desarrollar aplicaciones con el software System Generator para su implementación en FPGAs? Para dar respuesta al problema de investigación se propone como objetivo general: Desarrollar aplicaciones que ilustren las prestaciones que brinda el software System Generator para su implementación en FPGAs de Xilinx. Partiendo del objetivo general se derivan los siguientes objetivos específicos: • Caracterizar los FPGAs de Xilinx y el software System Generator para elaborar aplicaciones. • Identificar los principales campos en los que se utiliza System Generator en el mundo para la confección de aplicaciones. • Confeccionar aplicaciones usando System Generator para implementarlas en FPGAs. • Comprobar el funcionamiento de las aplicaciones desarrolladas en un FPGA. De los objetivos específicos surgen las siguientes interrogantes científicas: ¿Cuáles son las ventajas y desventajas que brinda el software System Generator para la implementación de aplicaciones en FPGAs? ¿Cuáles son las principales aplicaciones en las que se utiliza System Generator? ¿Qué aplicaciones confeccionar utilizando System Generator para montarlas en FPGAs? ¿Cómo comprobar el funcionamiento de las aplicaciones desarrolladas utilizando System Generator en un FPGA? Para realizar esta investigación se cuenta con un kit de desarrollo Nexys2 de Digilent el cual posee un FPGA Spartan-3E de Xilinx, con el software Matlab 7.9.0.529 (R2009b) y con el paquete Xilinx ISE Design Suite 12.1 que contiene el software System Generator. Para satisfacer los objetivos planteados el trabajo se dividió en: introducción, tres capítulos, conclusiones, recomendaciones y referencias bibliográficas. El primer capítulo aborda las características generales de los FPGAs y ofrece una introducción al software System Generator, sus características fundamentales, posibilidades.

(14) INTRODUCCIÓN. 4. que brinda de simulación, así como las principales aplicaciones en las que se utiliza este software en el mundo. En el segundo capítulo se desarrollan tres aplicaciones con el software System Generator que abarcan el trabajo con algunas interfaces disponibles en el kit de desarrollo Nexys2. Se realiza una introducción donde aparecen aspectos como el principio de funcionamiento, la utilidad práctica y se describe como se implementaron los subsistemas fundamentales de cada diseño. Por último, en el tercer capítulo, se comprueba el funcionamiento de las aplicaciones desarrolladas mediante la simulación en Simulink de cada sistema desarrollado y se muestran las aplicaciones funcionando en el kit Nexys2..

(15) CAPÍTULO 1. CARACTERIZACIÓN DE LOS FPGAS DE XILINX Y DEL SOFTWARE SYSTEM. 5. GENERATOR. CAPÍTULO 1. CARACTERIZACIÓN DE LOS FPGAS DE XILINX Y DEL SOFTWARE SYSTEM GENERATOR. Desde su introducción a mediado de la década de 1980, los FPGAs son cada vez más utilizados en la industria electrónica debido a su flexibilidad, reconfiguración y capacidad para ejecutar operaciones de forma paralela. El diseño de aplicaciones para implementar en estos dispositivos se realiza comúnmente mediante lenguajes de descripción de hardware. Sin embargo, en ocasiones los diseñadores necesitan herramientas de simulación que permitan no solamente realizar la descripción, sino evaluar la viabilidad y el desempeño de los sistemas implementados, lo más rápido y eficiente posible. Con este propósito se han creado herramientas de simulación y modelado de alto nivel, las cuales permiten mejorar y optimizar los tiempos de desarrollo e implementación de las aplicaciones. Una de estas herramientas es el software System Generator. En este capítulo se abordan las características generales de los FPGAs. Se ofrece una introducción al software System Generator, sus características fundamentales, posibilidades de simulación que brinda, así como una breve descripción de los bloques fundamentales. Además se muestran las principales aplicaciones en las que se utiliza este software en el mundo. 1.1. Los FPGAs de Xilinx: evolución y funcionamiento. Un FPGA es un dispositivo semiconductor que contiene bloques de lógica cuya interconexión y funcionalidad puede ser configurada mediante un lenguaje de descripción especializado. La lógica programable puede reproducir desde funciones tan sencillas como las llevadas a cabo por una compuerta lógica o un sistema combinacional, hasta complejos.

(16) CAPÍTULO 1. CARACTERIZACIÓN DE LOS FPGAS DE XILINX Y DEL SOFTWARE SYSTEM. 6. GENERATOR. sistemas en un chip. Un FPGA típico consiste en centenares o miles de bloques lógicos cuyas conexiones son programables. El desempeño de cada dispositivo depende del circuito contenido en su lógica de bloques y la eficiencia de sus interconexiones programadas. Los FPGAs son chips de silicio reprogramables que utilizan bloques de lógica preconstruidos y recursos para ruteo programables. Por tanto, pueden configurarse para implementar funcionalidades personalizadas en hardware sin tener que utilizar una tablilla de prototipos o un cautín. Solo es necesario desarrollar tareas de cómputo digital en software y compilarlas en un archivo de configuración que contenga la información de cómo deben conectarse los componentes. Anteriormente, se requería de profundos conocimientos de diseño de hardware digital para trabajar con la tecnología FPGA, sin embargo, el aumento de las herramientas de diseño de alto nivel está cambiando las reglas de programación de estos dispositivos. Las nuevas tecnologías convierten los diagramas, bloques gráficos, e incluso el código ANSI C a circuitos de hardware digital (Instruments, 2008). La adopción de los FPGAs en la industria ha sido impulsada por el hecho de que los FPGAs combinan lo mejor de los ASICs (Application Specific Integrated Circuits) y de los sistemas basados en procesadores. Ofrecen velocidades temporizadas por hardware y fiabilidad, pero sin requerir altos volúmenes de recursos para compensar el gran gasto que genera un diseño personalizado de ASIC. El silicio reprogramable tiene la misma capacidad de ajustarse que un software que se ejecuta en un sistema basado en procesadores, pero no está limitado por el número de núcleos disponibles. A diferencia de los procesadores, los FPGAs llevan a cabo diferentes operaciones de manera paralela, por lo que éstas no necesitan competir por los mismos recursos. Cada tarea de procesos independientes se asigna a una sección dedicada del chip, y puede ejecutarse de manera autónoma sin ser afectada por otros bloques de lógica. Como resultado, el rendimiento de una parte de la aplicación no se ve afectado cuando se agregan otros procesos (Instruments, 2008). Cualquier circuito de aplicación específica puede ser implementado en un FPGA, siempre y cuando esta disponga de los recursos necesarios. Las aplicaciones donde más comúnmente se utilizan los FPGA incluyen el procesamiento digital de señales, radio definido por software, sistemas aeroespaciales y de defensa, prototipos de ASICs, sistemas de imágenes.

(17) CAPÍTULO 1. CARACTERIZACIÓN DE LOS FPGAS DE XILINX Y DEL SOFTWARE SYSTEM. 7. GENERATOR. para medicina, sistemas de visión para computadoras, reconocimiento de voz, bioinformática, emulación de hardware de computadora, entre otras. Cabe notar que su uso en otras áreas es cada vez mayor, sobre todo en aquellas aplicaciones que requieren un alto grado de paralelismo (Microsistemas, 2011, Xilinx, 2012). El mercado de los FPGAs es competitivo, no obstante es liderado por las compañías Xilinx y Altera. A pesar de que Altera ha logrado importantes avances, Xilinx mantiene una amplia ventaja con el 52% del mercado (Microsistemas, 2011). La evolución de los FPGAs hasta la fecha ha seguido tres vías diferentes: a) Tecnológica Geometrías cada vez más pequeñas usando transistores más pequeños y rápidos, acompañada de costos cada vez menores por área. b) Estructural Orientación al diseño de sistemas generadores de acarreos, memorias, multiplicadores y procesadores embebidos. Interconexiones jerárquicas, control de impedancias de entrada/salida. c) Metodológica Disponibilidad de módulos sintetizables cada vez más complejos. Orientada hacia el diseño modular y en equipo. 1.1.1 Arquitectura básica de los FPGAs Cada FPGA está compuesto de un número finito de recursos predefinidos con interconexiones programables para implementar un circuito digital reconfigurable. La arquitectura de un FPGA como se muestra en la figura 1.1, consiste en arreglos de bloques lógicos que se comunican entre sí, a través de canales de conexión vertical y horizontal. Los bloques lógicos configurable (CLB) constan básicamente de una parte combinacional que permite implementar funciones lógicas y una parte secuencial formada por flip-flops, que permite sincronizar la salida con una señal de reloj externa, lo cual es útil para realizar circuitos secuenciales y la implementación de registros. La estructura de un bloque lógico varía de un fabricante a otro, sin embargo, la lógica combinacional se basa principalmente en Tablas de Búsqueda o Look-Up Tables (LUTs)..

(18) CAPÍTULO 1. CARACTERIZACIÓN DE LOS FPGAS DE XILINX Y DEL SOFTWARE SYSTEM. 8. GENERATOR. Figura 1.1. Estructura básica de un dispositivo FPGA (Morris y Ciletti, 2006). Una LUT es un componente de memoria que almacena una tabla de verdad. Las direcciones de la memoria son las entradas de la función lógica a implementar, y en cada localidad de dicha memoria se almacena el resultado de la combinación correspondiente de las entradas. En una LUT de n x 1 es posible implementar cualquier función lógica de n entrada. Los bloques de entrada/salida (IOB) son otro de los componentes particulares que tienen los FPGAs. Estos controlan el flujo de datos entre los pines de entrada/salida y la lógica interna del dispositivo. En diferentes familias de FPGAs, se dividen las entradas/salidas del integrado en bancos que se pueden configurar para tener una interfaz con lógica de diferentes estándares eléctricos de manera independiente. Los IOBs deben ser capaces de proveer una adecuada terminación en cuanto a impedancia se refiere, y de esta forma evitar reflexiones de las señales (Cárdenas, 2009). Para poder implementar circuitos lógicos, los elementos lógicos presentados anteriormente no solo deben configurarse adecuadamente sino que también deben conectarse entre sí. En general, las conexiones internas entre elementos de un FPGA pueden realizarse básicamente de tres formas:.

(19) CAPÍTULO 1. CARACTERIZACIÓN DE LOS FPGAS DE XILINX Y DEL SOFTWARE SYSTEM. 9. GENERATOR. -. Líneas directas: Tienen lugar entre bloques adyacentes.. -. Conexiones de propósito general: Se realizan a través de una matriz de interconexión cuando se desean conectar dos bloques no adyacentes. Su misión es conectar canales verticales y horizontales que permiten llegar al punto final de la conexión.. -. Líneas de largo recorrido: Suelen cubrir la pastilla a lo largo y ancho. Permiten conexiones con un retardo mucho menor que uniendo las anteriores.. 1.1.2 Kit de desarrollo Nexys2 La tarjeta Nexys2 es una plataforma de desarrollo basada en el FPGA Spartan3E de Xilinx. Posee un puerto USB 2.0 de alta velocidad, 16 Mbytes de memoria RAM (Random Access Memory) y ROM (Read Only Memory), varios dispositivos de entrada/salida y puertos (Figura 1.2) para el desarrollo de sistemas digitales. El puerto USB 2.0 provee energía a la tarjeta y una interfaz para la programación, así la tarjeta Nexys2 puede ser utilizada para crear una verdadera estación de diseño portable. Los diseños desarrollados en esta tarjeta pueden crecer fácilmente más allá de la misma, utilizando los cinco conectores de expansión que posee. La figura 1.2 muestra el diagrama en bloques de esta tarjeta.. Figura 1.2. Diagrama en bloques del kit Nexys2 (Digilent, 2008). Todas las señales accesibles por el usuario en la tarjeta son protegidas contra cortocircuitos, asegurando una larga vida de operación en cualquier ambiente. La tarjeta Nexys2 es.

(20) CAPÍTULO 1. CARACTERIZACIÓN DE LOS FPGAS DE XILINX Y DEL SOFTWARE SYSTEM. 10. GENERATOR. completamente compatible con todas las versiones de las herramientas de Xilinx ISE. Para más información consultar: (Digilent, 2008). 1.2. Características del software System Generator. La integración de las herramientas de diseño electrónico en entornos de desarrollo basados en modelos ha impulsado el auge de nuevas técnicas de diseño para dispositivos reconfigurables, facilitando la implementación de sistemas de procesamiento modulares y autónomos. Xilinx es pionera en el desarrollo de herramientas de este tipo, que facilitan el diseño de sistemas de procesamiento digital en una amplia variedad de FPGAs producidos por esta misma compañía (Xilinx, 2010a). System Generator es una herramienta de diseño de alto nivel desarrollada por Xilinx que permite el diseño basado en modelos en el entorno Matlab/Simulink para el desarrollo de sistemas de procesamiento digital en FPGAs. En el anexo I se recogen las recomendaciones de software y hardware necesarias para la instalación de esta herramienta. Matlab es un programa de cálculo numérico y visualización de datos para la resolución de problemas complejos planteados en la realización y aplicación de modelos matemáticos de ingeniería. Este software posee una extraordinaria versatilidad y capacidad para resolver problemas de matemática aplicada, física, química, ingeniería, finanzas y otras aplicaciones. Su base la constituye el cálculo matricial e integra análisis numérico, procesamiento de señales y visualización gráfica. Se utiliza en escuelas y centros universitarios, así como en departamentos de investigación y desarrollo de muchas compañías. Además se encuentra disponible para un amplio número de plataformas que operan bajo sistemas operativos Unix, Mac OS y Windows. Matlab dispone de herramientas adicionales que expanden sus prestaciones como Simulink, un software para modelar, simular y analizar sistemas dinámicos. Simulink proporciona una interfaz de usuario gráfica para construir los modelos como diagramas de bloques, utilizando operaciones con el ratón del tipo pulsar y arrastrar. Después de definir un modelo, se puede simular e interactuar con dicha simulación a través de los diferentes menús que ofrece el programa. Además, es posible cambiar los parámetros y ver de forma.

(21) CAPÍTULO 1. CARACTERIZACIÓN DE LOS FPGAS DE XILINX Y DEL SOFTWARE SYSTEM. 11. GENERATOR. inmediata lo que sucede tras el cambio; pudiendo transferir los resultados de la simulación al espacio de trabajo del programa Matlab, para su posterior procesamiento y visualización. Simulink incluye una amplia biblioteca de fuentes y herramientas de visualización que lo hacen ideal para el diseño de sistemas. Esto supone un cambio radical respecto a otras herramientas de simulación, que requieren una formulación de las ecuaciones en forma de lenguaje o programa. Como todos los blocksets de Simulink, System Generator se integra como una biblioteca de bloques que pueden ser conectados para crear modelos funcionales de un sistema dinámico (Figura 1.3). De esta forma, permite modelar, simular y analizar sistemas de procesamiento complejos y de alto rendimiento para una plataforma hardware específica, mediante un entorno flexible, robusto y fácil de utilizar. System Generator no puede considerarse como un sustituto de los lenguajes de descripción de hardware hasta la fecha, pero sí un potente complemento (Xilinx, 2010a).. Figura 1.3. Biblioteca de System Generator en Matlab/Simulink. La biblioteca de System Generator comprende desde los componentes más básicos de cada familia de FPGAs soportada como sumadores, multiplicadores y registros; hasta módulos más sofisticados que llevan a cabo tareas de procesamiento de más alto nivel como bloques.

(22) CAPÍTULO 1. CARACTERIZACIÓN DE LOS FPGAS DE XILINX Y DEL SOFTWARE SYSTEM. 12. GENERATOR. de corrección de errores para sistemas de comunicaciones, filtros, FFT (Fast Fourier Transform) y memorias. Todos los bloques están agrupados en librerías (Tabla 1.1) de acuerdo a función que realizan y algunos se encuentran en varias de ellas por ser comunes para la mayoría de los sistemas. Estos bloques aprovechan los generadores principales de Xilinx IP (Intellectual Property) para entregar resultados óptimos en la implementación hardware para el dispositivo seleccionado. Tabla 1.1. Bibliotecas de System Generator en Simulink. (Xilinx, 2010b) Librería Index. Descripción Todos los bloques en el Blockset de Xilinx.. Basic Elements. Control Logic. Bloques de elementos estándar para la construcción de lógica digital. Bloques de corrección de errores de uso común en los sistemas de comunicaciones digitales. Bloques de circuitos de control y máquinas de estado.. Data Types. Bloques para convertir tipos de datos.. DSP. Bloques de Procesamiento Digital de Señales.. Math. Bloques que implementan funciones matemáticas.. Memory. Bloques para la implementación y acceso a la memoria.. Shared Memory. Bloques para la implementación y acceso a la memoria compartida de Xilinx Bloques de Herramientas, por ejemplo, la generación de código (bloque System Generator), estimación de recursos, co-simulación, etc.. Communication. Tools. Los diseños desarrollados con System Generator pueden componerse de una gran variedad de elementos: bloques específicos de System Generator, código de un lenguaje de descripción de hardware tradicional como VHDL o Verilog y funciones derivadas del lenguaje de programación M de Matlab. Así, todos estos elementos pueden ser usados simultáneamente, simulados en conjunto y sintetizados para obtener todo un sistema de procesamiento de señales sobre un FPGA. Las restricciones que se deben tener en cuenta a la hora de incorporar estos elementos a un diseño pueden ser consultadas en: (Xilinx, 2010a)..

(23) CAPÍTULO 1. CARACTERIZACIÓN DE LOS FPGAS DE XILINX Y DEL SOFTWARE SYSTEM. 13. GENERATOR. Otro de los aspectos interesantes que presenta System Generator es la co-simulación hardware. Mediante esta se puede cargar el diseño en el FPGA, simularlo junto al resto del modelo en Simulink y observar el comportamiento del algoritmo directamente en hardware. Además es posible configurar y cargar diferentes tarjetas para poder usar el resto de componentes que acompañan al FPGA, fundamentalmente las memorias externas incluidas en las tarjetas. Esto dota de gran versatilidad al modelo y la simulación que se está realizando, pues es posible acceder, durante la simulación, a otros dispositivos de la placa que de otra manera no sería posible. Sin embargo esta característica no es explotada en esta tesis pues la Facultad no cuenta con el cable que permite conectar la computadora con la placa para llevar a cabo la co-simulación. Cuando se diseña con lógicas programables, el proceso desde la definición del circuito por el desarrollador hasta tenerlo funcionando sobre un FPGA implica varios pasos intermedios y en general se utilizan varias herramientas. Sin embargo, en System Generator todos los pasos del diseño incluyendo la síntesis (synthesis) y la ubicación e interconexión (place and route) son realizados automáticamente por el software para generar el fichero de programación (.bit) que será cargado en el FPGA (Xilinx, 2010a). Además de generar directamente el fichero de programación del FPGA seleccionado, System Generator también puede generar automáticamente el código HDL (puede ser VHDL o Verilog) y un proyecto Xilinx ISE (Integrated Software Environment) del modelo que se esté desarrollando, archivos de simulación, testbench, entre otros. El entorno Xilinx ISE es una herramienta de diseño de circuitos profesional que permite realizar un diseño completo basado en lógica programable. Incluye todas las etapas del flujo de diseño basado en FPGA necesarias como son: entrada del diseño, síntesis, implementación, verificación y configuración del dispositivo. Este entorno permite combinar diferentes técnicas de diseño para facilitar la labor de descripción del circuito. Como System Generator está integrado en el ambiente de Simulink, comúnmente para el diseño de un sistema se comienza creando un modelo utilizando una serie de bloques estándares de Simulink. Este puede ser diseñado usando precisión numérica de punto flotante y sin detalle de hardware. Una vez que la funcionalidad y el flujo de datos básico han sido creados, System Generator puede ser usado para especificar los detalles de.

(24) CAPÍTULO 1. CARACTERIZACIÓN DE LOS FPGAS DE XILINX Y DEL SOFTWARE SYSTEM. 14. GENERATOR. hardware del diseño que será implementado en el dispositivo de Xilinx. Después de comprobada la funcionalidad del diseño se puede generar el código. Para ello, System Generator invoca de forma automática al Xilinx Core Generator que genera los netlists altamente optimizados para los bloques en construcción y ejecuta las herramientas de compilación de Xilinx necesarias para generar el fichero de programación (.bit) (Domínguez et al., 2010). En la figura 1.4 se muestra el flujo de diseño creado por Moctezuma y Torres de System Generator.. Verificación del sistema. Síntesis. Simulación funcional. Implementación. Simulación temporal. Descarga. Verificación In-Circuit. Figura 1.4. Flujo de diseño en System Generator. (Moctezuma y Torres, 2010) 1.3. Principales campos de aplicación del software System Generator. Las posibilidades de este software de diseño, su flexibilidad y su compatibilidad con un gran número de FPGAs y herramientas de Xilinx, hace que su uso en la actualidad se extienda a diversos campos de la electrónica y las telecomunicaciones. El uso de esta herramienta es fundamental en centros de investigación y desarrollo en universidades y empresas donde se requiere probar algoritmos y crear prototipos de forma rápida, eficiente y con un bajo costo asociado. A continuación se muestran los principales campos donde se utiliza el software System Generator a partir de publicaciones científicas consultadas..

(25) CAPÍTULO 1. CARACTERIZACIÓN DE LOS FPGAS DE XILINX Y DEL SOFTWARE SYSTEM. 15. GENERATOR. Comunicaciones El vertiginoso desarrollo de las tecnologías de fabricación de dispositivos electrónicos ha marcado un importante avance en las comunicaciones digitales. Una tecnología que se ha visto beneficiada por este desarrollo es la de Radio Definido por Software (SDR). SDR es una tecnología aplicable en un amplio rango de áreas dentro la industria inalámbrica, capaz de proveer soluciones eficientes y comparativamente baratas a muchos problemas inherentes a las arquitecturas de radio más tradicionales. En esencia, SDR es un término utilizado para describir una tecnología de radio donde algunas o todas las funciones de la capa física inalámbrica son definidas por software (Pucker, 2010). Las expectativas, tanto de calidad de servicio como de tasa de bits, de los nuevos estándares de comunicaciones inalámbricas están llevando la teoría de la señal y la implementación de algoritmos en hardware a sus límites (Mendicute, 2008). En la actualidad, la implementación de la capa física de algunos estándares de comunicaciones inalámbricas en dispositivos lógicos programables como los FPGAs, ha ganado especial importancia por las prestaciones que brindan los mismos y la cantidad de herramientas de diseño disponibles. Los diseñadores se ven obligados a utilizar herramientas de software con una alta fiabilidad que ayuden a crear prototipos capaces de ajustarse a entornos cambiantes y ciclos de vida de productos más cortos. Empresas como Sandia National Laboratories en Nuevo México y BAE System desarrollan etapas de transmisión y recepción para equipos de comunicaciones utilizando la tecnología SDR con el software System Generator, pues con esta herramienta los diseñadores pueden verificar el diseño antes de su implementación haciendo uso de la amplia variedad de bibliotecas disponibles en Simulink. Esto les permite localizar los errores en etapas intermedias del proceso, cuando resulta más fácil y menos costoso solucionar los problemas. Además, según criterios de ingenieros que trabajan para estas empresas han visto reducido notablemente el tiempo de desarrollo utilizando el diseño basado en modelos en el entorno de Matlab/Simulink con respecto al diseño utilizando lenguajes de descripción de hardware como VHDL (Mathworks, 2011). Pero no solo estas empresas utilizan esta herramienta, una gran cantidad de trabajos del tema pueden ser consultados en Internet, donde utilizan el software System Generator para.

(26) CAPÍTULO 1. CARACTERIZACIÓN DE LOS FPGAS DE XILINX Y DEL SOFTWARE SYSTEM. 16. GENERATOR. la implementación de sistemas de comunicaciones en FPGAs de Xilinx. Etapas de modulación y demodulación con distintas técnicas digitales como QAM (Quadrature Amplitude Modulation) y PSK (Phase Shift Keying) en sus distintas variantes (16QAM, BPSK, QPSK), etapas de codificación, encriptación, sincronismo, entre otras, son implementadas con este software. Procesamiento de imágenes El procesamiento de imágenes es un campo muy extenso con un gran número de aplicaciones en la actualidad. Aunque la medicina no es la única que se vale de este campo para alcanzar éxitos, es en esta rama donde posee vital importancia. El procesamiento de imágenes está presente en una amplia variedad de equipos de diagnóstico y monitoreo como equipos de Rayos X, Imágenes por Resonancia Magnética (IRM), Tomografía Computarizada (CT) y equipos de Ultrasonido. Uno de los principales problemas a la hora de abordar la implementación de estos sistemas surge de la necesidad de cumplir requisitos cada vez más estrictos de velocidad de procesamiento, flexibilidad, costo económico, fiabilidad y tiempo de desarrollo (Toledo et al., 2007). Los algoritmos de procesamiento digital de imágenes presentan, en general, una gran carga computacional e imponen serias restricciones temporales para asegurar la operación en tiempo real. Por este motivo, la inclusión de estos algoritmos en sistemas empotrados con recursos de cálculo limitados requiere la aplicación de métodos que permitan acelerar su ejecución. El avance de las tecnologías de fabricación de circuitos integrados ha permitido el desarrollo de dispositivos lógicos programables (como los FPGAs) de elevadas prestaciones que proporcionan una solución alternativa a la implementación eficiente de este tipo de algoritmos, permitiendo asignar tareas de cálculo intensivas al hardware y explotar el paralelismo de los algoritmos (Garcés et al., 2011). Sin embargo el hardware no lo es todo, se necesitan poderosas herramientas de diseño que posibiliten la creación de prototipos de forma rápida, de modo que sea posible explorar una gran cantidad de configuraciones y algoritmos de procesamiento en poco tiempo. System Generator posee características que lo hacen ideal para el desarrollo de estos sistemas. Su integración con Simulink permite hacer uso de las bibliotecas de procesamiento de imágenes (Video and Image Processing Blockset) y de procesamiento de señales (Signal.

(27) CAPÍTULO 1. CARACTERIZACIÓN DE LOS FPGAS DE XILINX Y DEL SOFTWARE SYSTEM. 17. GENERATOR. Processing Blockset) para comprobar el diseño realizado y hacer los ajustes pertinentes. Además la co-simulación hardware brinda la posibilidad de visualizar de forma sencilla el comportamiento del algoritmo en el FPGA. En trabajos como el de (Garcés et al., 2011) se expresa que se encuentran desarrollando una biblioteca de bloques para el procesamiento de imágenes en System Generator cuyas posibilidades de configuración faciliten la optimización de los diseños y su adaptación a las necesidades de los usuarios. Implementación de Redes Neuronales Artificiales En cualquier rama de la ingeniería existe la necesidad de crear sistemas inteligentes que puedan tener autonomía a la hora de solucionar un problema concreto. El hecho de llevar a un dispositivo hardware modelos neuronales que permitan predecir el comportamiento de variables o clasificar características hacen que sea una temática interesante de estudio en la actualidad (Jaimes et al., 2011). Una Red Neuronal Artificial (RNA) es un modelo de procesamiento de información inspirado en el funcionamiento del sistema nervioso biológico. Este se compone de un gran número de elementos interconectados (neuronas) trabajando en armonía para resolver problemas específicos (Moctezuma y Torres, 2010). La teoría de las RNA ha brindado una alternativa a la computación clásica, para aquellos problemas, en los cuales los métodos tradicionales no han entregado resultados muy convincentes. Las aplicaciones más exitosas de las RNA son: el procesamiento de imágenes y de voz, reconocimiento de patrones, predicción, filtrado de señales, control y optimización de procesos (Reyes y Tapia, 2010). Las necesidades del mundo moderno de acelerar los procesos y reducir costos, han hecho que las investigaciones se centren en buscar la forma de implementar modelos teóricos en dispositivos físicos capaces de realizar las tareas solicitadas en el menor tiempo posible, con la mayor confiabilidad disponible y con el mayor grado de precisión y desempeño alcanzable. La implementación de las RNA en dispositivos lógicos programables ayuda a desarrollar investigaciones ingenieriles de avanzada y sigue siendo una temática actual de investigación. El uso de la herramienta System Generator para el diseño de redes.

(28) CAPÍTULO 1. CARACTERIZACIÓN DE LOS FPGAS DE XILINX Y DEL SOFTWARE SYSTEM. 18. GENERATOR. neuronales es un tema novedoso. Trabajos como (Jaimes et al., 2011, Moctezuma y Torres, 2010, Reyes y Tapia, 2010) coinciden en que esta potente herramienta ofrece un ambiente de diseño amigable y bloques funcionales que pueden ser interconectados de forma muy sencilla para desarrollar redes neuronales complejas. Radioastronomía La radioastronomía es la rama de la astronomía que estudia los objetos celestes y los fenómenos astrofísicos a través del análisis de ondas de radio. Este campo permite a los científicos la observación de fenómenos astronómicos que a menudo son indetectables en regiones del espectro electromagnético con una longitud de onda mayor que la de la luz visible. Tradicionalmente, el desarrollo de instrumentos de tiempo real para el procesamiento de los datos provenientes de los radiotelescopios implica contratar ingenieros con mucha experiencia en el diseño e implementación de sistemas electrónicos personalizados. Estos proyectos pueden tomar más de una década en completarse con el consiguiente costo asociado y en ocasiones la tecnología queda obsoleta en poco tiempo por el rápido crecimiento de la industria de la electrónica (Siemion, 2011). En la Universidad de California el Center for Astronomy Signal Processing and Electronics Research (CASPER) ha desarrollado una librería basada en Simulink que simplifica y acelera el desarrollo de instrumentos de radioastronomía. La misma consta de bloques funcionales comunes para la mayoría de los instrumentos de radioastronomía desarrollados con el software System Generator, por lo que una vez verificada la funcionalidad del diseño mediante la simulación, este puede ser implementado directamente en un FPGA de Xilinx. Como resultado, ingenieros y científicos pueden construir y desplegar sofisticados instrumentos a un fragmento del costo del hardware personalizado en poco tiempo. La librería es open source por lo que los usuarios pueden contribuir al desarrollo de nuevos componentes para la misma. Uno de los instrumentos desarrollados con la librería CASPER es el espectrómetro digital Fly’s Eye utilizado para buscar pulsos de alta energía en el espacio por el Allen Telescope Array (ATA) en el norte de California..

(29) CAPÍTULO 1. CARACTERIZACIÓN DE LOS FPGAS DE XILINX Y DEL SOFTWARE SYSTEM. 19. GENERATOR. 1.4. Conclusiones del capítulo. En este capítulo se ofreció un acercamiento a la estructura de los FPGAs producidos por Xilinx. Se resumieron los aspectos más importantes del software System Generator, una herramienta de alto nivel que se integra a Matlab/Simulink para el diseño, simulación e implementación de circuitos en FPGAs. También se mostraron algunas de las principales aplicaciones donde se utiliza este software, demostrándose lo versátil que es para la implementación de complejos sistemas digitales..

(30) CAPÍTULO 2. APLICACIONES DESARROLLADAS UTILIZANDO SYSTEM GENERATOR. 20. CAPÍTULO 2. APLICACIONES DESARROLLADAS UTILIZANDO SYSTEM GENERATOR. Como se vio en el capítulo anterior, System Generator posee una biblioteca de modelos mediante bloques parametrizables asociados a funciones aritméticas, lógicas y operaciones complejas para el procesamiento de señales, en un entorno gráfico, que facilita la descripción del algoritmo que se va a implementar. Esta característica hace que este software sea utilizado por ingenieros para el desarrollo de sistemas de comunicaciones, procesamiento de imágenes, instrumentos de radioastronomía, entre otros. En este capítulo se desarrollan tres aplicaciones con el software System Generator. Para una mejor comprensión de las mismas, se realiza una introducción donde aparecen aspectos como el principio de funcionamiento y la utilidad práctica. Además, se describe como se implementaron los subsistemas de cada diseño. Las aplicaciones seleccionadas abarcan el trabajo con algunas de las interfaces disponibles en el kit de desarrollo Nexys2. 2.1. Confección de un cronómetro digital. El cronómetro es un reloj o una función de reloj utilizada para medir fracciones temporales, normalmente breves y precisas (La Guía Metas, 2007). La resolución de un cronómetro representa el período de tiempo más pequeño que el instrumento puede medir o indicar. Los cronómetros pueden activarse con métodos automáticos, con menor margen de error sin necesidad de una persona que accione un botón. Algunos de estos sistemas son: el corte de un haz luminoso o la detección de un transceptor. Los cronómetros se usan fundamentalmente en competiciones deportivas, aunque algunas ramas de la ciencia y la tecnología se valen de estos para realizar mediciones de tiempo precisas. El diseño de un cronómetro digital es uno de los proyectos que más se orienta en centros de estudio donde.

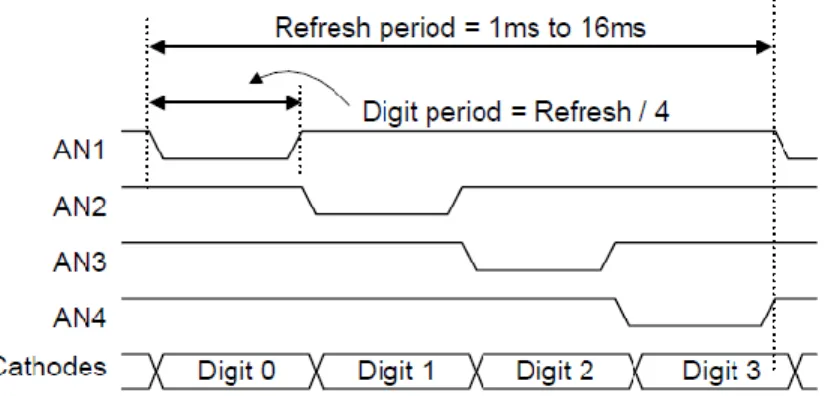

(31) CAPÍTULO 2. APLICACIONES DESARROLLADAS UTILIZANDO SYSTEM GENERATOR. 21. se imparten disciplinas relacionadas con la electrónica digital y microprocesadores, pues ayuda a los estudiantes a desarrollar habilidades en el empleo de circuitos sincrónicos y el trabajo con bases de tiempo precisas. Cada cronómetro está compuesto por cuatro elementos fundamentales: fuente de poder, base de tiempo, contador y un indicador, como se muestra en la figura 2.1. El diseño y construcción de cada componente depende del tipo de cronómetro que se desea construir (La Guía Metas, 2007).. Fuente de poder Base de tiempo (oscilador de referencia). Contador. Indicador. Figura 2.1. Subsistemas que componen un cronómetro digital (La Guía Metas, 2007). La fuente de poder provee la energía que alimenta la circuitería del oscilador, el contador y el indicador para su correcto funcionamiento. El oscilador de referencia es el que produce la señal de reloj usada por el cronómetro para medir el intervalo de tiempo. La precisión con que trabaja el circuito depende de este bloque, de aquí la importancia que tiene la correcta calibración del mismo. El módulo de contadores es el encargado de medir el período de tiempo transcurrido desde que se inició el conteo. La forma de visualizar la información varía de un diseño a otro, pero la gran mayoría utiliza pantallas LCD (Liquid Crystal Display) o pantallas siete segmentos como la que se utiliza en este trabajo. La tarjeta Nexys2 consta de un display siete segmentos ánodo común de cuatro dígitos (Figura 2.2). Los ánodos de los siete LEDs (Light Emitting Diodes) que forman cada dígito están unidos formando un ánodo común, pero los cátodos permanecen separados. Las señales de los cuatro ánodos comunes son para habilitar cada dígito del display. Los cátodos de los segmentos similares de cada dígito están unidos formando siete nodos etiquetados CA-CG (así, por ejemplo, los cuatro cátodos “D” de cada dígito están agrupados en un nodo llamado “CD”). Estas siete señales constituyen las entradas del display. Las señales se multiplexan de tal forma que los cátodos son comunes a todos los dígitos, pero solo se ilumina aquel cuyo ánodo está habilitado..

(32) CAPÍTULO 2. APLICACIONES DESARROLLADAS UTILIZANDO SYSTEM GENERATOR. 22. Figura 2.2. Display siete segmentos del kit Nexys2 (Digilent, 2008). Para mostrar correctamente los números es necesario implementar un circuito que controle el escaneo del display. Este circuito maneja la habilitación del dígito con el correspondiente patrón (Figura 2.3) en una sucesión continua a una razón lo suficientemente alta que el ojo humano puede detectar. Cada dígito es iluminado la cuarta parte del tiempo, pero el ojo no puede percibir el oscurecimiento de un LED antes de que este se vuelva a iluminar, así el dígito aparece completamente iluminado. Si la frecuencia de refrescamiento está por debajo de 45Hz, se comenzará a percibir parpadeo en el display. Por tanto, es necesaria una frecuencia de refrescamiento entre 60Hz y 1kHz para que cada dígito aparezca con el brillo adecuado e iluminado continuamente (Digilent, 2008).. Figura 2.3. Diagrama de tiempo para display siete segmentos de cuatro dígitos (Digilent, 2008). 2.1.1 Implementación en la herramienta de simulación El cronómetro digital desarrollado tiene una resolución de un segundo y un valor máximo de cuenta de una hora. Para la visualización se utilizan los cuatro displays siete segmentos disponibles en el kit Nexys2, dos para mostrar los segundos (de 0 a 59) y dos para mostrar.

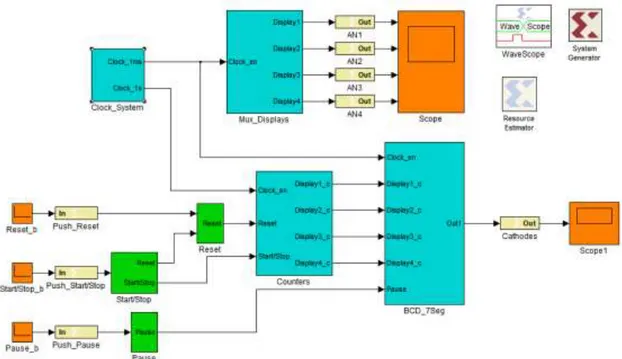

(33) CAPÍTULO 2. APLICACIONES DESARROLLADAS UTILIZANDO SYSTEM GENERATOR. 23. los minutos (de 0 a 59). La señal de reloj proviene del oscilador de 50MHz con que funciona el FPGA. Esta señal es utilizada para obtener las bases de tiempo de un milisegundo y un segundo necesarias para el correcto funcionamiento del circuito. El diseño realizado se muestra en la figura 2.4. Los valores mostrados en los displays son generados por cuatro contadores conectados en cascada de modo que se van incrementando cuando el contador anterior llega al final del valor de conteo. La conversión de decimal a siete segmentos se realizó con una memoria ROM que almacena los valores en siete segmentos de cada dígito en la posición de memoria correspondiente al valor del mismo en decimal, de esta forma los contadores van seleccionando en la memoria los valores a mostrar en el display. Por otra parte, para la correcta visualización se generan cuatro señales que permiten hacer la multiplexación en tiempo de los displays utilizando la base de tiempo de un milisegundo. De este modo cada dígito se mantiene encendido un milisegundo logrando una frecuencia de refrescamiento adecuada.. Figura 2.4. Cronómetro realizado en System Generator. El sistema dispone de un pulsador para iniciar y detener la cuenta, uno para congelar el tiempo, y otro que da un reset a los contadores en caso de ser necesario. Al pulsar el botón Pause_b se congela el tiempo actual de forma que sobre los displays se muestra dicho.

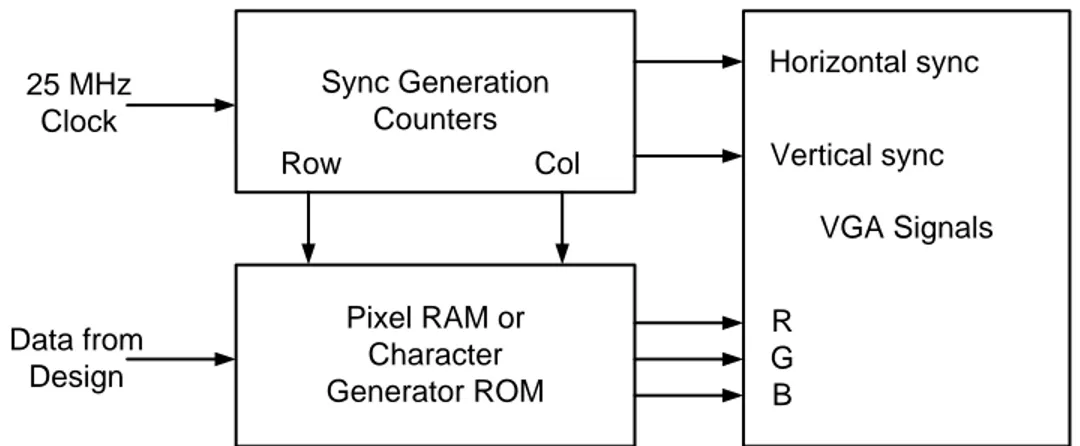

(34) CAPÍTULO 2. APLICACIONES DESARROLLADAS UTILIZANDO SYSTEM GENERATOR. 24. instante de tiempo mientras que el cronómetro sigue contando internamente. Al volver a pulsar Pause_b se muestra el tiempo transcurrido actualmente. Para congelar el tiempo mostrado, las salidas de los contadores se conectan a registros controlados por una señal de habilitación. Cuando la señal de habilitación de estos registros está activa, su salida refleja el valor actual de cuenta. Si por el contrario la señal de habilitación está desactivada, la salida de los contadores no se actualiza en los registros por lo que se visualizará en los displays el valor de cuenta detenido. Todas las funciones que controlan a los pulsadores se implementaron con el bloque MCode. 2.2. Confección de un controlador VGA. VGA (Video Graphics Array) es un estándar para mostrar video introducido a finales de la década de 1980 en las computadoras IBM. El VGA original soportaba una resolución de 640x480 con 16 colores en modo gráfico. El modo VGA sigue siendo el estándar utilizado en el arranque de los ordenadores, hasta que se hacen cargo del control de los gráficos los controladores de la tarjeta de video instalada. Se trata del último estándar de video impuesto por IBM, y a partir de él se empezaron a desarrollar modelos que cada vez ofrecían más calidad y prestaciones, movidos en gran medida por el auge de los juegos de ordenador (Almalasi, 2008). Un circuito controlador VGA como se observa en la figura 2.5 debe generar las señales de temporización vertical y horizontal y coordinar el envío de los datos de video basado en el reloj de píxel. El reloj de píxel define el tiempo disponible para representar la información de un píxel en la pantalla. Los datos de video vienen típicamente de una memoria de video, con uno o más octetos asignados a cada localización del píxel. El controlador debe poner un índice en la memoria cuando los haces se mueven a través de la pantalla, recuperar y aplicar estos datos a la misma en el tiempo exacto que el haz electrónico se está moviendo a través de un píxel dado..

(35) CAPÍTULO 2. APLICACIONES DESARROLLADAS UTILIZANDO SYSTEM GENERATOR. 25 MHz Clock. 25. Horizontal sync. Sync Generation Counters Row Col. Vertical sync VGA Signals. Data from Design. Pixel RAM or Character Generator ROM. R G B. Figura 2.5. Diagrama en bloques de un controlador VGA (Hamblen et al., 2006). Un monitor VGA común puede ser controlado utilizando solo cinco líneas: dos de sincronismo y tres señales analógicas correspondientes a los colores rojo, verde y azul (RGB). Las señales analógicas correspondientes a cada color permiten variar la intensidad de los mismos simplemente variando su voltaje. Combinando correctamente el valor de tensión aplicado a las tres líneas analógicas se puede obtener el color deseado como se muestra en la Tabla 2.1 para un controlador con tres bits de color. Tabla 2.1. Combinaciones posibles con tres bits de color. Rojo. Verde. Azul. 0 0 0 0 1 1 1 1. 0 0 1 1 0 0 1 1. 0 1 0 1 0 1 0 1. Color resultante Negro Azul Verde Cian Rojo Magenta Amarillo Blanco. El circuito de sincronización de video genera la señal de sincronismo horizontal que especifica el tiempo que demora escanear una línea horizontal, y la señal de sincronismo vertical que especifica la frecuencia de refrescamiento del monitor. Para una resolución de 640x480 con un reloj de píxel de 25MHz y una frecuencia de refrescamiento de 60Hz, se derivan las señales de sincronismo mostradas en las figuras 2.6 y 2.7 para el circuito horizontal y vertical respectivamente..

(36) CAPÍTULO 2. APLICACIONES DESARROLLADAS UTILIZANDO SYSTEM GENERATOR. pixel (0,0). 26. pixel (639,0). black area display area. pixel (0,479). pixel (639,479). deflection sawtooth h_video_on pixel count. 0. hsync. left border (48). display (640). 639. 655. 751. 799. right border (16) front porch retrace (96) one horizontal scan (800). left border (48) back porch. Figura 2.6. Diagrama de tiempo para una línea horizontal (Chu, 2008). Un circuito decodifica la salida de un contador de sincronismo horizontal controlado por el reloj del píxel, para generar la señal de sincronismo hsync (Figura 2.6). Asimismo, la salida de un contador de sincronismo vertical que incrementa con cada pulso de hsync se utiliza para generar la señal de sincronismo vsync (Figura 2.7). Ambos contadores pueden ser usados para localizar un píxel en cualquier posición de la pantalla y formar una dirección en la memoria RAM de vídeo cuya información se corresponda con el color del píxel. De esta forma se logra disminuir notablemente la complejidad del circuito. 480 horizontal scan lines. v_video_on line count. vsync. top border (33). 0. 479. display (480). 489. bottom border (10) front porch retrace (2). 491. 524. top border (33) back porch. one vertical scan (525). Figura 2.7. Diagrama de tiempo para la exploración vertical (Chu, 2008)..

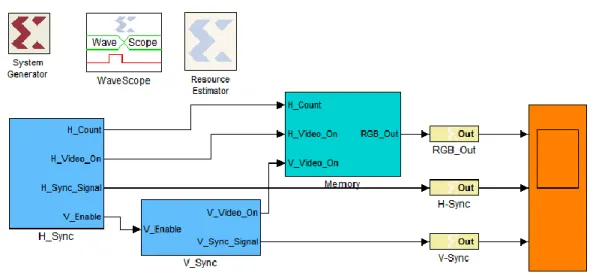

(37) CAPÍTULO 2. APLICACIONES DESARROLLADAS UTILIZANDO SYSTEM GENERATOR. 27. Es habitual que para el diseño las especificaciones no se den en tiempos, sino que se da la frecuencia de reloj de los píxeles. Con esta frecuencia, se especifica el número de píxeles de la señal de sincronismo horizontal y el número de líneas para el sincronismo vertical. 2.2.1 Implementación en la herramienta de simulación El esquema diseñado en System Generator se muestra en la figura 2.8. Para comprobar el funcionamiento se utilizó la interfaz disponible en el kit Nexys2 la cual utiliza 10 señales para crear un puerto VGA con ocho bits de color y dos señales estándares de sincronismo. Las etapas de sincronismo se implementaron utilizando dos contadores, uno que contara hasta 800 utilizando el reloj de píxel para generar el sincronismo horizontal y otro que contara 525 líneas para el barrido vertical. Un circuito decodificador es el encargado de generar las señales de sincronismo y de habilitación de video como las mostradas en las figuras 2.6 y 2.7.. Figura 2.8. Controlador VGA desarrollado con System Generator. Para verificar el funcionamiento del controlador se generó un patrón de barras verticales que muestra ocho colores en orden decreciente de luminancia desde el blanco (máxima luminancia) hasta el negro (mínima luminancia) como se puede observar en la figura 2.9. El patrón de pruebas es uno de los elementos más utilizados por los ingenieros en el control de los parámetros que determinan la calidad de la imagen reproducida. El uso de estos patrones permite realizar una inspección visual inmediata de la calidad de la imagen reproducida sobre la pantalla del monitor de imagen..

(38) CAPÍTULO 2. APLICACIONES DESARROLLADAS UTILIZANDO SYSTEM GENERATOR. 28. Figura 2.9. Patrón de pruebas utilizado. Los colores generados se corresponden con las combinaciones presentadas en la Tabla 2.1. Como todas las líneas horizontales del patrón de barras son iguales la información de color de una línea se cargó en una memoria ROM manejada por el contador horizontal que extrae los valores en instantes precisos de tiempo. De este modo no fue necesario utilizar el contador vertical para localizar una fila específica en la memoria de video. 2.3. Confección de un modulador y demodulador 16QAM. La Modulación de Amplitud en Cuadratura (QAM) es una modulación digital en la que el mensaje está contenido tanto en la amplitud como en la fase de la señal transmitida. Se basa en la transmisión de dos mensajes independientes por un único camino. Esto se consigue modulando en amplitud (ASK, Amplitude Shift Keying) de forma independiente, dos portadoras que tienen la misma frecuencia pero que están desfasadas entre si 90º. La señal modulada en QAM es el resultado de sumar ambas señales ASK. Esto supone la formación de dos canales ortogonales en el mismo ancho de banda, con lo cual se mejora en eficiencia. La importancia de este sistema de modulación se debe a la gran cantidad de aplicaciones asociadas a ella. Es empleada por módems para alcanzar velocidades superiores a los 2400bps (por ejemplo V.22 bis y V.32). Es la modulación empleada en muchos sistemas de transmisión de televisión, microondas y satélite. También es la base de la modulación TCM (Trellis Coded Modulation), que consigue velocidades de transmisión elevadas combinando la modulación con la codificación de canal. Además es utilizada por módems ADSL (Asymmetric Digital Subscriber Line) que trabajan en el bucle de abonado, a frecuencias.

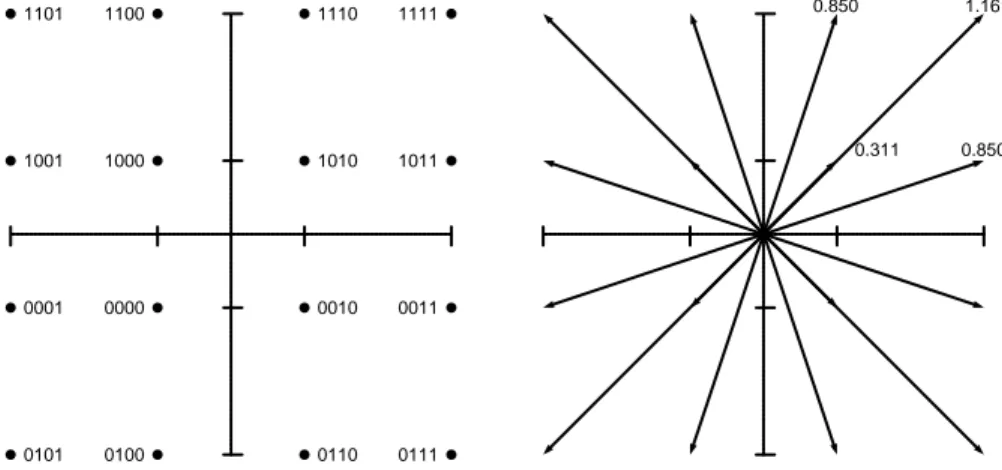

(39) CAPÍTULO 2. APLICACIONES DESARROLLADAS UTILIZANDO SYSTEM GENERATOR. 29. situadas entre 24kHz y 1104kHz, para obtener velocidades de hasta 9Mbps, modulando en QAM diferentes portadoras. 2.3.1 Características del modulador El 16QAM es un sistema M-ario donde M=16, que actúa sobre los datos de entrada en grupos de cuatro (24 = 16). El diagrama en bloques para un transmisor 16QAM se muestra en la figura 2.10. Los datos de entrada binaria en serie se dividen en cuatro canales: I, I’, Q, Q’. La tasa de bits de cada canal es igual a un cuarto de la tasa de bits de entrada. .. Los bits I y Q determinan la polaridad a la salida de los convertidores de niveles y los bits I’ y Q’ determinan la magnitud. En consecuencia, los convertidores de niveles generan una señal PAM (Pulse Amplitude Modulation). Dos polaridades y dos magnitudes son posibles a la salida de cada convertidor que son: ±0.22 V y ±0.821 V con lo que se obtiene una señal con cuatro niveles de amplitud. Las señales PAM generadas modulan las portadoras en fase y en cuadratura, en los moduladores de producto. Luego el sumador lineal combina la salida de los moduladores de producto de canal I y Q y produce las 16 condiciones de salida necesarias para el esquema de modulación presentado. I I’. fb/4. Convertidor de Nivel 2a4. PAM. Modulador balanceado. fb/4 sen wct. Entrada de datos binarios. Q. Q’. I. Oscilador de la portadora de referencia. I’. Sumador lineal. Salida 16QAM. 90° fb/4. fb/4. cos wct Q’ Q. Convertidor de Nivel 2a4. PAM. Modulador balanceado. Figura 2.10. Diagrama a bloques para el modulador 16QAM (Tomasi, 2003). Los símbolos a transmitir son números complejos que pueden representarse de la forma . Así, el alfabeto lo forman el conjunto de números complejos que pueden ser transmitidos. Este alfabeto se puede representar en el plano complejo, formando la.

(40) CAPÍTULO 2. APLICACIONES DESARROLLADAS UTILIZANDO SYSTEM GENERATOR. 30. constelación de la modulación. En la figura 2.11 se presenta el diagrama de constelación y fasorial de un modulador 16QAM. 1101. 1100. 1110. 1111. 1001. 1000. 1010. 1011. 0001. 0000. 0010. 0011. 0101. 0100. 0110. 0111. 0.850. 0.311. 1.161. 0.850. Figura 2.11. Diagrama de constelación y fasorial 16QAM (Tomasi, 2003). 2.3.2 Características del demodulador En la figura 2.12 se muestra el diagrama en bloques de un demodulador 16QAM. El divisor de potencia dirige la señal de entrada a los detectores de producto I y Q, y al circuito de recuperación de portadora. Este último circuito reproduce la señal original del oscilador de referencia de transmisión. La portadora recuperada debe ser coherente, en frecuencia y en fase, con la portadora de referencia de transmisión. La señal de entrada se mezcla con la portadora recuperada en el detector de producto I, y con la portadora en cuadratura en el detector de producto Q. A la salida del filtro paso bajo en los canales I y Q, se obtiene una señal PAM con cuatro niveles de amplitud que se alimentan al convertidor de cuatro a dos niveles. Las salidas del convertidor del canal I son los bits I e I’, mientras que las del convertidor del canal Q son los bits Q y Q’. El circuito paralelo serie convierte los pares I/I’ y Q/Q’ en una corriente de bits I’, I, Q’ y Q en serie..

(41) CAPÍTULO 2. APLICACIONES DESARROLLADAS UTILIZANDO SYSTEM GENERATOR. Canal I. Detector de producto. LPF. Convertidor de Nivel 4a2. 31. I’ I. sen wct Entrada 16QAM. Recuperación de la portadora sen wct. Q. Q’. I. I’. Salida de datos binarios. 90° cos wct Canal Q. Detector de producto. LPF. Convertidor de Nivel 4a2. Q Q’. Figura 2.12. Demodulador 16QAM (Tomasi, 2003). La señal 16QAM que se recibe tiene valores de amplitud y fase que varían dependiendo de la combinación de símbolos transmitida. La señal 16QAM transmitida a la salida del sumador lineal tiene la forma general:. Para ilustrar el proceso de demodulación llevado a cabo en el detector de producto y el filtro paso bajo la descripción matemática del modelo es la siguiente: Para el canal I a la salida del detector de producto se obtiene que. Donde el primer término señalado es la señal en banda base y el segundo es la componente de alta frecuencia centrada en. que es eliminada por el filtro paso bajo.. Repitiendo el procedimiento para el canal Q se obtienen resultados similares a los obtenidos en (3)..

(42) CAPÍTULO 2. APLICACIONES DESARROLLADAS UTILIZANDO SYSTEM GENERATOR. 32. 2.3.3 Implementación en la herramienta de simulación La implementación en System Generator del modulador y el demodulador se realizó basándose en los esquemas mostrados anteriormente. Ambos diseños se combinaron en un solo proyecto para probar la funcionalidad del sistema pues la Facultad no cuenta con los conversores D/A y A/D para la tarjeta disponible. Para evitar introducir señales externas al FPGA, la entrada binaria y las portadoras se generan internamente con bloques de System Generator para luego implementarlas en el FPGA.. Salida 16QAM. Al Demodulador. Figura 2.13. Modulador 16QAM diseñado con System Generator. La figura 2.13 muestra el diseño del modulador realizado con System Generator. Para generar la entrada binaria aleatoria se utilizó el bloque LFSR (Linear Feedback Shift Register). Este bloque genera la misma entrada binaria siempre ya que es un registro de desplazamiento determinístico y la secuencia de valores producidos está completamente determinada por el estado actual o el estado anterior. La secuencia tiene un período de repetición, es decir, la secuencia vuelve a generarse y se repite indefinidamente. Las portadoras en fase y en cuadratura se generaron con una frecuencia de 500kHz..

(43) CAPÍTULO 2. APLICACIONES DESARROLLADAS UTILIZANDO SYSTEM GENERATOR. 33. Para el diseño en System Generator del demodulador se partió del esquema representado en la figura 2.12. Sin embargo, la complejidad que trae acompañada la etapa de recuperación de la portadora se sale de los objetivos de este trabajo, por lo que se supone que se conoce la portadora en el receptor y se implementan los demás bloques funcionales. Las portadoras en fase y en cuadratura son las mismas que las generadas para el modulador. La figura 2.14 muestra los componentes en System Generator del demodulador 16QAM.. Entrada 16QAM. Del Modulador. Figura 2.14. Componentes del demodulador en System Generator. Para el diseño del filtro se utilizó el bloque FDATool disponible en la librería de System Generator que facilita el diseño de filtros digitales. La implementación se llevó a cabo con el bloque FIR Compiler 5.0 el cual toma los valores de los coeficientes exportados por el bloque FDATool para la realización del filtro. 2.4. Conclusiones del capítulo. En este capítulo se realizó una caracterización de las aplicaciones que se implementaron utilizando System Generator, a través de las cuales se demuestran las facilidades que brinda este software para el diseño digital..

(44) CAPÍTULO 3. IMPLEMENTACIÓN Y COMPROBACIÓN DE LAS APLICACIONES. 34. CAPÍTULO 3. IMPLEMENTACIÓN Y COMPROBACIÓN DE LAS APLICACIONES. En el capítulo anterior se brindó una introducción teórica de las aplicaciones desarrolladas y de la implementación de las mismas en el software System Generator. En el desarrollo de este capítulo se describe brevemente la herramienta utilizada para cargar el fichero de programación en el FPGA, se comprueba el correcto funcionamiento de las aplicaciones desarrolladas mediante la simulación en Simulink y se muestran las aplicaciones implementadas en el kit Nexys2. 3.1. Implementación en el FPGA de las aplicaciones confeccionadas. Todo sistema desarrollado con System Generator debe incluir un bloque del mismo nombre que esta herramienta. Este bloque es el encargado de proporcionar el control del sistema, los parámetros de las simulaciones, e invocar el generador de código. En el mismo, se especifican características del proyecto tales como la familia del dispositivo en el que se va a implementar el diseño, la frecuencia de operación del circuito, la herramienta utilizada para la síntesis, el lenguaje de descripción de hardware y el tipo de compilación a utilizar. En cada uno de los bloques de System Generator, se deben ajustar ciertos parámetros como frecuencia, número de bits, nombre de pines de la tarjeta, entre otros. Para esto, es muy importante que se conozca muy bien la estructura, así como las especificaciones de la tarjeta que se está utilizando, de esta manera se evitará cometer errores. Una vez que se han configurado los bloques es posible realizar una simulación exitosa. Después de comprobada la funcionalidad del diseño se puede generar el fichero de programación (.bit) que luego será cargado en el FPGA con otra herramienta..

Figure

Documento similar

Abstract: This paper reviews the dialogue and controversies between the paratexts of a corpus of collections of short novels –and romances– publi- shed from 1624 to 1637:

entorno algoritmo.

Missing estimates for total domestic participant spend were estimated using a similar approach of that used to calculate missing international estimates, with average shares applied

Por lo tanto, en base a su perfil de eficacia y seguridad, ofatumumab debe considerarse una alternativa de tratamiento para pacientes con EMRR o EMSP con enfermedad activa

The part I assessment is coordinated involving all MSCs and led by the RMS who prepares a draft assessment report, sends the request for information (RFI) with considerations,

Ciaurriz quien, durante su primer arlo de estancia en Loyola 40 , catalogó sus fondos siguiendo la división previa a la que nos hemos referido; y si esta labor fue de

Para denegación hegeliana del mal: «Así como no existe lo fal- so, no existe el mal, es objetada primero por Sade y luego por la subjetividad romántica: en la mé- dula de la

Entre las limitaciones que se establecen en el acceso al divorcio, des- taca la recogida en el artículo cincuenta y uno, donde se expone que el hombre que haya expresa su intención